9月4日,在台北舉行的「Semicon Taiwan 2024」展會上,三星電子記憶體事業本部部長(社長)李正培作為主題演講嘉賓,介紹了三星的HBM優勢。

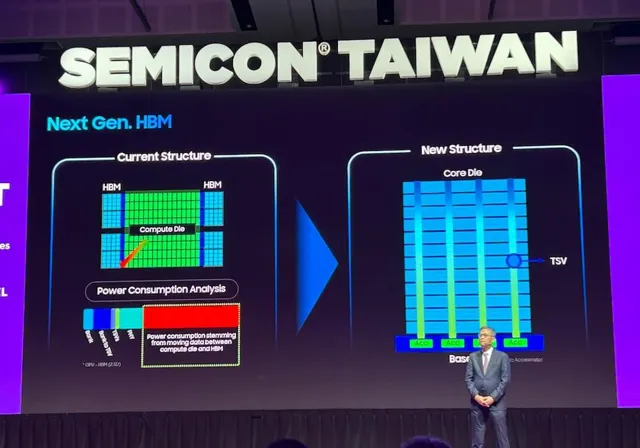

李正培表示,目前AI時代遇三大挑戰,即能耗、因記憶體頻寬限制帶來的AI效能限制,以及儲存容量限制。由於頻寬和記憶體容量需求增加,目前的HBM構架已經無法滿足需求,加上HBM能耗較高,即數據傳輸與GPU間的能耗較高,因此三星將推出新的HBM構架,以減少當中傳輸。

三星提出的新的解決方案與SK海麗仕一樣,雖然HBM3E及之前的HBM都是采用DRAM制程的基礎裸片(Base Die),采用2.5D 系統級封裝,但是到HBM4都計劃將DRAM Base Die 改成Logic Base Die,以及3D封裝,以推動效能和能效進一步提升。

具體來說,這個Logic Base die是連線AI加速器內部圖形處理單元(GPU)和DRAM的必備元件,位於DRAM的底部,主要充當GPU和記憶體之間的一種控制器,並且這個Logic Base Die與之前的Base Die不同,它可以讓客戶自行設計,可以加入客戶自己的IP,有利於HBM實作客製化,從而讓數據處理更為高效。預計可以將功耗大幅降低至之前的30%。

三星在HBM4以前的DRAM制程Base Die,都是由自家內存部門負責制造,但隨著下一代的HBM4的Base Die轉向 Logic Base Die,這部份則將交由邏輯制程晶圓代工廠制造,三星儲存部門則負責制造核心的DRAM Die,因此未來內存制造商和晶圓代工業者與客戶的合作關系越來越緊密。

李正培表示,「僅靠現有的記憶體工藝來提高HBM的效能是有限的,必須結合邏輯制程才能最大限度地提高 HBM 效能。」不過,這個Logic Base Die的制造並不會限制客戶交由三星設計(幫助客戶加入客戶自己的IP或者選擇三星提供的IP)或一定要使用三星晶圓代工廠來代工,客戶可以自由選擇。

但是,李正培也指出,三星在生產客製 HBM 方面具有優勢,因為三星同時擁有半導體設計和晶圓代工能力,並且在市場上擁有強大的地位。

另外,三星也將推進新的HBM封裝技術,將透過HCB連線技術,使堆疊增加30%、熱阻(thermal resistance)減少20%,再透過3D封裝實作更大頻寬、更大容量、能耗更少。比如Logic Base Die和記憶體之間的頻寬可以達到70.5TB/s。

最後,李正培強調,三星可以一次性完成從Logic Base Die設計、代工制造、封裝的所有工作,可以提供一站式的服務。也可以與很多生態系夥伴共同合作,滿足客戶不同需求,可使用不同夥伴的設計和服務。

相比之下,SK海麗仕在邏輯制程的能力上存在一定的欠缺,為了解決這一問題,SK海麗仕也計劃和台積電進行合作。雖然此前SK海麗仕自己制造Base Die,但從第6代的HBM4開始,將會委托台積電生產Logic Base Die,以進一步提升效率。

編輯:芯智訊-浪客劍