全文速覽

目前常見的SiC外延技術有化學氣相沈積(CVD)、液相外延生長(LPE)、分子束外延生長(MBE)等,當前,CVD是主流技術,具備較高生長速率、能夠實作可控摻雜調控等優點。CVD外延生長通常使用矽烷和碳氫化合物作為反應氣體,氫氣作為載氣,氯化氫作為輔助氣體,或使用三氯氫矽(TCS)作為矽源代替矽烷和氯化氫,在約1600℃的溫度條件下,反應氣體分解並在SiC襯底表面外延生長SiC薄膜。2022年美國Wolfspeed公司已成功實作8英寸SiC外延產品的量產。市場上主流的量產產品主要是650、1200、1700V金氧半場效晶體管(MOSFET)器件用6英寸外延產品。

天科合達團隊基於十多年在SiC底材料制備技術研究和產業推廣經驗的積累,2022年開始啟動SiC外延技術研發,重點針對1200V車規級MOSEET器件用SiC外延材料進行研發和產業化工作。 近日,天科合達團隊在【人工晶體學報】發表了題為【碳化矽同質外延質素影響因素的分析與綜述】的綜述論文。 文章對外延生長過程中晶體缺陷如何轉化並影響器件效能進行了系統分析和綜述,並基於北京天科合達半導體股份有限公司(天科合達)量產的高質素6英寸SiC襯底,探討了常見缺陷,如BPD、層錯、矽滴和Pits等的形成機理及其控制技術,並對Σ-BPD的產生機理和消除方法進行研究,最終獲得了厚度和濃度片內均勻性良好、缺陷密度低的外延產品,完成了650和1200V外延片產品的開發和產業化工作。

圖文導讀

1. SiC外延層的摻雜濃度控制

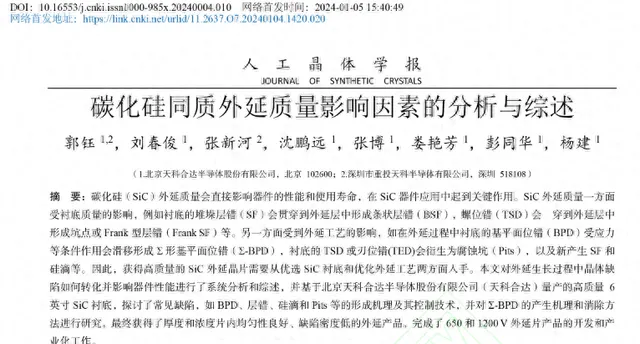

本團隊采用水平式外延生長方法,三氯氫矽和乙烯作為反應氣源,氮氣作為摻雜氣體,氫氣作為載氣,氫氣和氣作為驅動托盤旋轉的氣源,生長厚度適用於1200V的SiC基MOSFET用SiC外延層。透過調整摻雜氮氣在中心和邊緣分布比例、托盤旋轉的速度以及旋轉氣體中氯氣與氫氣的比例,最佳化外延工藝的C/Si比等生長參數,實作SiC外延層摻雜濃度以及均勻性的有效控制,圖1是量產1000片的厚度和濃度均勻性統計數據,C/Si比在1.0~1.2、溫度在1600~1650C和壓力在100mbar的工藝條件下,統計的外延產品100%達到厚度均勻性小於3%、濃度均勻性小於6%。

2. SiC 外延層的缺陷控制研究

根據晶體缺陷理論,SiC外延材料的主要缺陷可歸納為4大類:點缺陷、位錯(屬於線缺陷)、層錯(屬於面缺陷)和表面缺陷(屬於體缺陷)。

2.1 點缺陷

SiC外延材料的點缺陷主要有矽空位、碳空位、矽碳雙空位等缺陷,它們在禁帶中產生深能階中心,影響材料的載流子壽命。在輕摻雜的SiC 外延層中,點缺陷產生的深能階中心濃度通常在5E12~2E13 cm-3,與外延生長條件特別是C/Si 比和生長溫度相關。

2.2 位錯缺陷

SiC 材料的位錯包括螺位錯(TSD)、刃位錯(TED)和基平面位錯(BPD)。微管是伯氏向量較大的螺位錯形成的中空管道,可認為是一種超螺位錯。SiC 外延層的位錯缺陷基本都和襯底相關,大部份微管和螺位錯會復制到外延層中,在合適的工藝條件下,部份微管分解為單獨的螺位錯,形成微管閉合,只有一小部份TSD(通常<2%)轉為Frank 型層錯;襯底TED基本都會復制到外延層中。

BPD位錯主要源於襯底中BPD向外延層的貫穿,通常偏4º 4H-SiC襯底中大部份BPD位錯(>99%)在外延過程中會轉化為TED位錯,只有少於1%左右的BPD會貫穿到外延層中並達到外延層表面。在後續器件制造中,BPD主要影響雙極型器件的穩定性,如出現雙極型退化現象。在正精靈通電流的作用下,BPD可能會延伸至外延層演變成堆壘層錯(SF),造成器件正精靈通電壓漂移。由於刃位錯對器件效能的影響要小得多,所以提高SiC外延生長過程中BPD轉化為TED的比例,阻止襯底中的BPD向外延層中延伸對提高器件的效能十分重要。

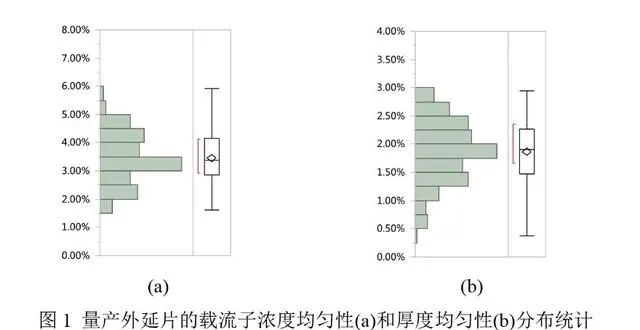

在生長過程中,在應力等條件作用下,BPD很容易在襯底和外延層界面上沿著台階流法線方向發生滑移,形成界面位錯(interfacial dislocations,滑移方向取決於BPD的伯氏向量及應力方向。特定條件下,成對BPD同時發生滑移,會形成Σ-BPD。在研發過程中也觀察到過該缺陷,其典型形貌如圖2所示,Photoluminescence 檢測BPD形貌如圖3(a),對外延片進行KOH腐蝕後形貌如圖3(b)所示,可以看到一個Σ-BPD包含兩條界面位錯,其長度可以達到毫米級,在其尾部存在兩個BPD。Σ-BPD形成機理示意圖如圖3(c)所示,其起源於襯底的BPD對,其伯氏向量方向剛好相反,滑移過程中形成兩條界面位錯和2個半環位錯(half-loop arrays,HLAs)。半環位錯的長度不一,決定於其驅動力大小,影響滑移的驅動力主要是溫場的不均勻性。

圖2 Σ-BPD 形貌圖(a)、氫氧化鉀腐蝕坑圖(b)和形成機理示意圖(c)

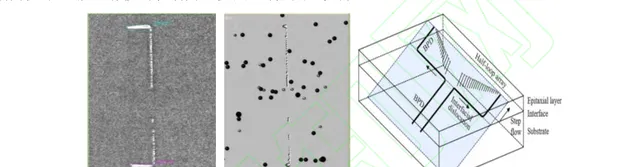

針對外延BPD,研究團隊在快速外延生長的基礎上最佳化外延層緩沖層工藝視窗,目前可以實作BPD 密度小於0.1 cm-3 的外延層批次制備,如圖3所示。

圖3 外延片的BPD分布及其控制

2.3 層錯缺陷

SiC外延層中的層錯包括兩大類,一類來源於襯底的層錯和位錯缺陷,襯底的層錯會導致外延層形成Bar-shaped SFs,襯底的部份TSD會形成Frank SFs;另一類層錯為生長層錯(in-grown SFs),是外延生長過程中產生的,與襯底質素沒有關系。目前,大多數外延層錯屬於第二類,這些層錯中絕大部份為Shockley SFs,是透過在基平面中的滑移產生的。

降低外延生長速率、原位氫氣刻蝕最佳化、增加生長溫度、改善襯底質素都可以有效降低層錯數量,天科合達已經可以提供Shockley SFs 密度小於0.15 cm-2的6英寸SiC襯底。

2.4 表面缺陷

SiC外延層表面缺陷尺度比較大,一般透過光學顯微鏡可以直接觀察到,包括掉落物、三角形缺陷、「胡蘿蔔」缺陷、彗星缺陷、矽滴和淺坑。

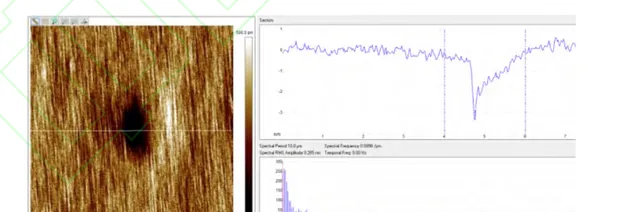

表面缺陷與器件效能的影響目前也已經有了較多的研究報道,除淺坑缺陷外,其他表面缺陷基本都會對器件的效能產生一定的不利影響,導致器件擊穿電壓降低或者反向漏流增加。淺坑(Pits)是4H-SiC外延層表面出現在TSD位錯頂端的小凹陷或小坑狀的形貌缺陷,其寬度尺度小於10 μm。TED在外延層表面引起的小坑尺寸遠小於TSD誘發的小坑尺寸,很難被觀察到。圖4是典型的淺坑AFM 形貌。

圖4 外延表面寬度和深度分別為2和4 nm的淺坑的AFM形貌

Ohtani、Noboru等則利用TUNA技術研究了Pits和Large Pits的產生機理,認為寬度在幾微米、深度在14 nm左右的Large pits是由TSD產生,而寬度在1 μm、深度在3-4 nm的Pits由TED產生。

降低Pits的主要途徑包括:優選TSD數量較少的優質襯底、降低碳矽比和降低外延生長速率。目前市場上主要的商業化襯底中TSD的密度為小於1000/cm-3。本研究團隊已經可以提供TSD密度小於300/cm-3的6英寸SiC襯底。透過采用優質襯底,調整外延工藝,可以將Pits數量從103降低到50以內。

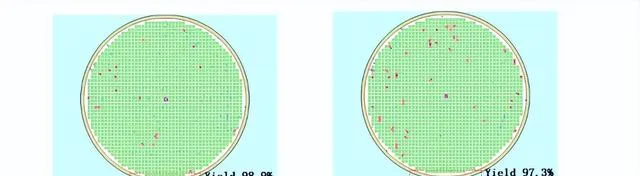

綜合來看,SiC外延層缺陷一方面取決於襯底結晶質素以及表面加工質素,另一方面受制於外延生長工藝視窗的最佳化,需要綜合考慮各種缺陷的調整方案。基於研究團隊量產的高質素6英寸SiC襯底,透過大量的實驗研究,可以有效控制住SiC外延的各種缺陷,完成650V和1200V外延片產品開發和產業化工作。圖5是典型的650V和1200V外延片產品缺陷mapping圖,3mm×3mm良品率分別為98.9%和97.3%。

圖5 650 V和1200 V外延片,3 mm×3 mm良品率分別為98.9%和97.3%

展 望

SiC外延在產業鏈中起著承上啟下的重要作用,一方面透過不斷積累對SiC材料的效能認知和改良,一方面透過器件的不斷叠代驗證,最終提升外延品質,推動SiC器件的套用。本文采用天科合達自有的商業化6英寸襯底,在4H SiC同質外延過程中,研究了外延層中BPD、層錯、矽滴和Pits缺陷的控制,並對Σ-BPD的產生機理和消除進行研究, 最終獲得厚度均勻性小於3%、濃度均勻性小於6%、表面粗糙度小於0.2m、良品率大於96%、BPD密度小於0.1cm的外延產品。 目前從本團隊的研發進度來看,透過對工藝溫度、C/Si比和長速等參數最佳化使得濃厚度分別控制在3%和2%以內,BPD的密度可以控制在0.075cm以內,但仍需要大量的外延數據進行工藝穩定性驗證。

論文連結:https://link.cnki.net/urlid/11.2637.07.20240104.1420.020