7月15日訊息,AMD近日在美國洛杉磯舉行的技術日活動中公布了「North Star」(北極星)計劃,未來推出的 Ryzen AI PC芯片將可支持以每秒100個Token的速度在本地執行300億個參數的大型語言模型(LLM),實作 3000 的語意長度,並且第一個Token生成的延遲要低於100毫秒。

但是,要實作AMD提出的這個目標並不容易,這需要硬體和軟體效能上的巨大提升。要知道AMD最新推出的代號為「Strix Point 」的AI PC芯片Ryzen AI 300系列在以 4bit 精度執行70億參數的大語言模型,每秒只能生成20個Token,並且第一個Token的生成延遲高達1-4秒。

如果要本地支持以每秒生成100個Token的速度執行 300 億參數的大模型,「North Star」不僅需要邏輯面積更大、效能更強的 NPU ,這對於提升 TOPS 或 FLOPS 肯定會有所幫助——尤其是在首次令牌延遲方面,但是在本地執行大型語言模型時,所需要的記憶體容量和頻寬也極為重要。

在這方面,AMD的Strix Point 的大語言模型效能在很大程度上受到其 128 位記憶體匯流排的限制——當選擇采用 LPDDR5x 配對時,其頻寬在一般 120-135 GBps 左右,具體取決於記憶體的速度。

理論上來說,一個真正的 300 億參數模型,量化為4bit,將消耗大約 15GB 的記憶體,並且需要超過 1.5 TBps 的頻寬才能達到每秒 100 個令牌的目標。作為參考,這與配備 HBM2 的 40GB Nvidia A100 PCIe 卡的頻寬大致相同,但功率要大得多。

這意味著,如果不進行最佳化以降低模型的要求(比如采用記憶體壓縮技術),AMD未來的SoC將需要更快、更高容量的LPDDR來達到芯片設計者的目標。

人工智慧的發展速度快於芯片

AMD 從事 SoC 開發的高級研究員和芯片設計工程師Mahesh Subramony對於這些挑戰表示,「我們知道如何到達那裏,雖然有可能設計出能夠實作AMD今天目標的部件,但如果沒有人能負擔得起使用它,或者沒有任何東西可以利用它,那就沒有多大意義了。」

「如果一開始就說每個人都必須擁有一輛法拉利,那麽汽車就不會激增。你必須首先說每個人都有一台很棒的機器,然後你首先展示你可以負責任地用它做什麽,「他解釋道。

「我們必須建立一個滿足 95% 人需求的 SKU,」他繼續說道。「我寧願擁有一台價值 1,300 美元的膝上型電腦,然後透過雲端來執行我的 300 億參數模型。今天這還是便宜的。」

在展示 AI PC 的價值方面,AMD 非常依賴其軟體合作夥伴。對於像 Strix Point 這樣的產品,這在很大程度上意味著需要微軟的支持。「當 Strix Point 最初開始時,我們與微軟的這種深度合作在某種程度上真正推動了我們的邊界,」他回憶道。

但是,雖然軟體可以幫助指導新硬體的發展方向,但開發和提升新芯片可能需要數年時間,Subramony解釋說。「Gen AI 和 AI 用例的發展速度遠快。」

自 ChatGPT 首次亮相以來,已經有兩年的時間來持續演變,Subramony 表示 AMD 現在對計算需求的發展方向有了更好的了解——這無疑是 AMD 制定這一目標的部份原因。

克服瓶頸

有幾種方法可以解決記憶體頻寬挑戰。例如,LPDDR5 可以換成高頻寬記憶體——但正如 Subramony 所指出的那樣,這樣做並不完全有利,因為它會大大增加成本並降低 SoC 的功耗。

「如果我們無法獲得 300 億個參數的模型,我們需要能夠獲得提供相同保真度的東西。這意味著在訓練中需要進行改進,以嘗試首先使這些更小的模型,「Subramony解釋說。

好訊息是,有很多方法可以做到這一點——這取決於你是想優先考慮記憶體頻寬還是容量。

一種可能的方法是按照 Mistral AI 的 Mixtral 使用混合專家 (MoE) 模型。這些 MoE 本質上是一組相互協同工作的較小模型。通常,完整的 MoE 會被載入到記憶體中,但由於只有一個子模型處於活動狀態,因此與同等大小的單片模型架構相比,記憶體頻寬需求大大降低。

由六個 50 億參數模型組成的 MoE 只需要略高於 250 GBps 的頻寬即可實作每秒 100 個Token的目標——至少精度為4bit。

另一種方法是使用推測解碼——一個小型輕量級模型生成草稿的過程,然後將其傳遞給更大的模型以糾正任何不準確之處。AMD表示,這種方法在效能上有相當大的改進,但它並不一定能解決大語言模型需要大量記憶體的事實。

如今,大多數模型都是在 Float 16 或 FP16 數據型別中訓練的,它們每個參數消耗兩個字節。這意味著一個 300 億參數的模型需要 60GB 的記憶體才能以原始精度執行。

但是,由於這對絕大多數使用者來說可能並不實用,因此將模型量化為 8bit 或 4bit 精度的情況並不少見。這犧牲了準確性並增加了AI幻覺的可能性,但將您的記憶體需求減少到四分之一。這也是AMD現有AI PC芯片如何以每秒20個Token的速度執行70億個參數模型的關鍵。

新形式的加速可以提供幫助

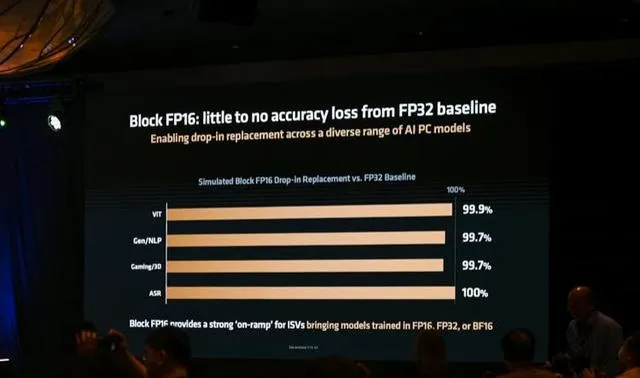

作為一種折衷方案,從 Strix Point 開始,AMD的XDNA 2 NPU 將支持新的Block FP16 數據型別。因為傳統的 INT8 應對目前的需求似乎已經有點力不從心,但是使用 FP32 又太過於浪費浪費,相對而言,采用 FP16 可以實作更高的算力,並且精度也足夠使用,但是依然會占據不小的頻寬。於是, AMD 選擇將 FP16 以及 INT8 融合打造成為 Block FP16 數據型別,結合了16bit數據的高精度和 8bit位數據的高效能,它只需要每個參數9bit——它能夠透過取 8 個浮點值並使用一個共享指數來做到這一點。根據 AMD 的說法,Block FP16 能夠達到與原生 FP16 幾乎無法區分的精度,同時僅比 Int8 占用略多的空間。

更重要的是,AMD稱該Block FP16 數據型別不需要重新訓練模型來利用它們——現有的 BF16 和 FP16 模型無需量化步驟即可工作。

但是,除非普通膝上型電腦開始配備48GB或更多的記憶體,否則AMD仍然需要找到更好的方法來縮小模型的占用空間。

雖然沒有明確提及,但不難想象 AMD 未來的 NPU 和/或整合顯卡會增加對 MXFP6 或 MXFP4 等較小的浮點格式的支持。目前AMD 的 CDNA 數據中心 GPU 也將支持 FP8,而 CDNA 4 將支持 FP4。

無論如何,隨著大語言模型開始向邊緣部署,PC 硬體似乎將在未來幾年發生巨大變化。

編輯:芯智訊-浪客劍 部份資料來源:The register