本文由半導體產業縱橫(ID:ICVIEWS)編譯自semiengineering

自動緩解熱問題成為異構設計中的首要任務。

3D-IC 和異構芯片將使物理布局工具發生重大改變,其中Chiplet 的放置和訊號的布線會對整體系統的效能和可靠性產生重大影響。

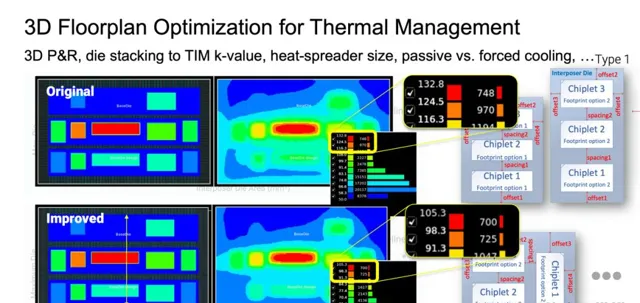

EDA 供應商非常清楚這些問題,並正在努力尋找解決方案。3D-IC 面臨的最大挑戰是散熱。邏輯通常會產生最多的熱量,而將邏輯芯片堆疊在其他邏輯芯片之上需要一種方法來散熱。在平面 SoC 中,這通常依賴散熱器或基板來處理。但在 3D-IC 中,需要減薄基板以盡量縮短訊號必須傳輸的距離,這會降低基板的傳熱能力。此外,熱量可能會滯留在芯片之間,因此散熱器不再備選。解決這個問題的方法是仔細配置不同的層,以便熱量分散到整個芯片上,或限制其在可以有效去除熱量的區域,這需要內建到自動化工具中。

Alphawave Semi 技術長 Tony Chan Carusone 表示:「向Chiplet 設計範式的過渡將影響現代布局布線設計流程,需要最佳化芯片之間的邏輯分區。這意味著基於芯片的系統的布局布線設計流程必須考慮多芯片整合、異構技術的潛力,並管理高密度芯片間互連的復雜性。這將需要了解不同制造和封裝技術提供的可能性和限制。」

經過數十年關於堆疊芯片的討論和 PowerPoint 演示,芯片行業已經沒有其他選擇了。芯片制造商已經在設計邏輯芯片堆疊和儲存芯片堆疊,並且隨著平面縮放的成本不斷增加,依賴某種類別的高級封裝和Chiplet 的系統設計是提高效能的最佳選擇,尤其是對於人工智能和其他高效能計算套用。

事實上,Yole 預測,從 2025 年開始,大多數伺服器芯片將使用Chiplet 構建,超過 50% 的批次客戶端 PC 將使用Chiplet 。這些數碼增加了對適應工具和工作流程需求的緊迫性。

布局規劃、布局、時鐘和布線是布局布線流程的四個主要階段。布局規劃探索發生在流程的早期,設計師將大型功能模組放置在芯片的不同區域,確定連線性,以及應該將哪個模組放在什麽旁邊。在此階段,模組具有將整個芯片區域劃分為粗分區的邊界。然後將標準單元作為定義的模組放置在每個邊界內。這些是遵守代工廠設計審查手冊中規定的小型庫單元。然後,它們根據本地連線透過互連相互布線。從總體上看,布局規劃步驟包含頂層連線的抽象檢視。

「在實際布局中,你是在對所有標準單元和宏進行詳細布局,」Cadence 產品管理組總監 Vinay Patwardhan 說道。「布線是連線它們的下一步。每到下一個階段,設計中的資訊都會越來越多。」

關於材料的基本決定,例如是否使用銅或光互連,是在早期探索階段或系統設計階段,甚至在平面規劃之前就已簽署的。

雖然這些步驟仍然按照傳統順序執行,但遊戲已經從經典棋局轉變為三維國際象棋。Synopsys 3D-IC 產品管理高級總監 Kenneth Larsen 表示:「現在有點復雜了。當我們談論 2.5/3D 以及向多芯片設計的過渡時,芯片之間的距離非常近,這帶來了許多新挑戰。當我們構建具有多個矽芯片的系統時,它們會非常緊密地連線在一起。它們可能堆疊在一起,並且會相互影響。其中一個問題是向系統供電。另一個問題是熱問題,因為距離很近。熱問題正在成為一階效應,而將零件放入布局規劃中的位置可能會影響設計中的熱量或溫度逸出。」

現在,所有這些都發生在三維空間中,設計中必須考慮到每個維度。Patwardhan 說:「現在,你不僅要考慮平面檢查,還要考慮放置物體與頂層和底層之間的相互作用,而不是只考慮平面檢查。在 3D-IC 堆疊芯片設計中,下層很多時候位於高級封裝的頂部,它與旁邊的 HBM 或其他儲存元件通訊,也與位於其頂部的物體通訊。你需要在 z 維度上觀察來自頂部芯片的耦合效應,觀察增加的電阻率,還要觀察存在同步時鐘的跨芯片的時序路徑。必須在放置流程的早期對兩個芯片之間的緊密通訊進行建模,在規劃芯片間連線流程時也是如此。」

這裏還有另一個重要方面需要考慮。「由於這些都是堆疊的金屬連線,因此金屬層之間的高導電性,會產生煙囪效應,在高功率密度區域可能會出現非常高的散熱量,」Patwardhan 說。「你可能滿足了時序或功率要求,但你可能沒有將熱作為一級效應考慮在內,現在你必須這樣做了。」

熱效應

人們越來越意識到熱效應(尤其是 3D 結構中的熱串擾)的重要性,這影響了設計團隊在此過程中的工作方式,打破了專業之間的壁壘。「熱問題一直是一個難題,」Larsen 說。「以前,你把它丟給專家,他會回應說,‘我們有一個熱問題,你需要限制芯片。’但現在,我們在設計過程中更早地引入了這些多物理效應的模擬,比 10 年前更早。」

西門子 EDA 研發總監 Kai-Yuan (Kevin) Chao 對此表示贊同。「物理設計中的熱規劃至關重要,因為大多數高效能 CPU 都具有加速和功率節流功能,以管理硬限晶體管結溫,從而確保芯片可靠性。簡而言之,使用平面圖進行最壞情況下的功率瓦特熱模擬的固定狀態,其意義不如在多個細分市場中模擬目標套用工作負載的意義,這些工作負載在不同內核和記憶體上執行,在該產品的冷卻使用下以各種組合執行。」

減少熱傳感器之間的節流裕度對於測量最關鍵工作負載引起的熱點非常重要。這決定了不同處理元件之間的距離,以及/或者如何劃分和優先處理各種操作。

Chao 指出:「由於電壓/頻率上下限的持續時間會影響效能和計算吞吐量,因此還需要瞬態熱功率斜坡建模和內部模擬調整溫度敏感參數(如泄漏)。」 整合穩壓器電感器和用於封裝設計和冷卻設計系統的走線也需要來自芯片設計的早期功率和熱圖,以協調組裝和產品釋出。因此,從 RTL 前架構階段到最終的流片前布局階段,物理平面圖(包括 I/O)和一致的功率瓦特收斂也很重要。」

圖 1:布局規劃與熱管理的相互作用。來源:Synopsys

甚至在設計師深入研究復雜的多物理場之前,布局規劃就可以提示哪裏可能存在熱問題。Arteris 產品管理和行銷副總裁 Andy Nightingale 表示:「一旦我們在螢幕上看到布局檢視並開始進行 NoC 設計,我們就可以看到哪裏存在擁塞點。這些高密度連線可以被視為設計中的熱點。」

所有這些都凸顯了為什麽 EDA 公司鼓勵使用者shift left 。Patwardhan 說:「如果你在進行訊號完整性感知布線,你必須在流程早期進行建模。你的模型有多好將決定你在設計階段結束時的準確性有多強。我們必須在流程的早期階段進行一些額外的簽核檢查或熱分析檢查,以及訊號和電源完整性分析。因此,如果我們談論的是單元級別的多芯片布局,無論它們是 2.5D 配置,還是堆疊芯片配置,許多系統級簽核檢查都必須在實施流程的早期進行建模。我們必須想出新的抽象方法,一些新的方法讓布局環境處理多個物件,一次最佳化更多參數,並做得足夠好,以便在有工程變更單 (ECO) 時不必重新開啟每個設計。從執行時間的角度或設計方法的角度來看,過早地將所有東西都納入進來並不實際,但我們可以在早期做足夠多的工作,以確保減少第一次透過後的叠代。」

展望 AI 未來

大家一致認為 EDA 已經是 AI 的一種,因為它一直是人類設計師基於演算法的輔助工具。不過,工具仍在不斷發展。EDA 供應商現在正在考慮擴充套件,例如為工具提供生成式 AI 副駕,以及更多地整合多物理模擬,同時開發專門用於處理多芯片和多維結構的設計引擎。

希望人工智能能將預測智能帶入傳統的布局布線。「我們已經擅長將先進演算法整合到 NoC 設計中,以實作各種最佳化,」Nightingale 說道。「下一步發展是基於歷史數據(甚至可能是實時分析)預測和最佳化平面規劃和布局布線結果。我們與生態系合作夥伴之間也需要進行跨領域的密切合作,以盡更多努力使設計保持在給定的約束範圍內。」

學術界也在提供幫助。麻省理工學院剛剛宣布了一種新的基於人工智能的方法,命名為虛擬節點圖神經網絡 (VGNN),使用虛擬節點來表示聲子,以加快對材料熱效能的預測。該論文的作者聲稱,僅在個人電腦上執行 VGNN 就能在幾秒鐘內計算出幾千種材料的聲子色散關系。

結論

當今的Chiplet 、系統和封裝設計人員面臨著更多的技術多樣性和系統協同最佳化要求。「基板更大、更復雜,包括中介層和埋入基板的矽橋,它們需要 EDA 路由器處理不同層次材料之間快速增長的路線連線,並采用特定的設計規則和高速電氣和熱機械約束來提高生產率,」西門子的 Chao 表示。「此外,特殊的布線要求需要 EDA 創新,例如基板電容器和光學元件。細間距混合鍵合使單時鐘周期互連能夠在垂直跨芯片 3D 規劃中進行單元級時序和 I/O 布局。盡管如此,增加封裝中芯片中的晶體管需要更高效的電力傳輸和散熱。例如,台積電在其未來的 HPC/AI 3D-IC 配置中添加了 IVR。包括液體冷卻在內的整合散熱器解決方案在 NVIDIA 的新產品中得到了共同最佳化。」

功率和散熱是日益嚴峻的挑戰。「除了為滿足 2nm 以下熱設計需求而引入的背面供電網絡外,如果產品設計中包含整合封裝/系統液體冷卻,熱感知布局和布局規劃要求(例如多芯片模組微通道冷卻協同設計)可能會重新出現,」Chao 繼續說道。「在由多個利益相關者共同擁有的協同開發過程中,具備多物理場意識的早期物理設計將非常有益,因為在驗證後的Chiplet 組裝階段,不切實際的假設可能會帶來非常昂貴的修復成本。」

在最佳化 3D-IC 設計流程之前,還有很長的路要走。「我們現在才剛剛開始這段旅程,」Cadence 的 Patwardhan 說道。「我們開發了一些相當不錯的演算法,可以同時進行 3D 布局、3D 平面規劃、熱感知 3D 平面規劃和布局。但是現在設計界和 EDA 界的每個人都非常保守,為堆疊芯片設計留出了額外的余地,因為我們正處於流程開發和早期測試芯片的階段。在很短的時間內,我們將從我們的學習中研發最佳化的流程,就像我們在 finFET 和 GAA 型晶體管時代快速發展一樣。現在,堆疊芯片只是增加了一個維度的額外挑戰。我們很快就能為復雜的 3D-IC 設計提出最佳化且完全自動化的 3D 布局和布線流程,這只是時間問題。」

*聲明:本文系原作者創作。文章內容系其個人觀點,我方轉載僅為分享與討論,不代表我方贊成或認同,如有異議,請聯系後台。