電子封裝金屬微凸點制備技術研究進展

王淩雲 鄭 康

(廈門大學薩本棟微米納米科學技術研究院)

摘要:

起著電互連、熱傳遞和機械支撐等重要作用的金屬微凸點是基於面積陣列封裝的關鍵。以球柵陣列封裝(Ball Grid Array Packaging, BGA)、芯片尺度封裝(Chip Scale Packaging, CSP)以及倒裝芯片封裝(Flip Chip Packaging, FCP)為代表的面積陣列封裝形式憑借矽片利用率高、互連路徑短、訊號傳輸延時短以及寄生參數小等優點迅速成為當今中高端芯片封裝領域的主流。然而,不同套用領域的微凸點具有尺寸跨度大、材料範圍廣的特點,很難有一種技術能實作全尺寸範圍內不同材料金屬微凸點的制備。文中綜述了當前主流的微凸點制備技術,包括每種技術的優缺點及其適用範圍、常見微凸點材料等,最後對當下微凸點制備技術的發展趨勢進行了展望。

引言

隨著電子資訊科技的飛速發展,電子產品不斷向微型化、多功能化和高整合化的方向發展。在不斷增長的需求推動下,微電子封裝技術經歷了插孔元件時代、表面貼裝時代、面積陣列時代和2.5D/3D封裝時代。

自20世紀90年代以來,集成電路進入了超大規模階段,單顆芯片的引腳數高達上千個。傳統的雙列直插封裝(Dual In-line Packaging, DIP)和方形扁平封裝(Quad Flat Packaging, QFP)在不增加整體尺寸的情況下只能不斷縮減引腳尺寸及間距,當引腳數超過500時,微小的安裝誤差就可能導致焊錫橋接和斷路。在此背景下,以面積陣列排布輸入/輸出(Input/Output, I/O)凸點的封裝形式—球柵陣列封裝(Ball Grid Array Packaging, BGA)、芯片尺度封裝(Chip Scale Packaging, CSP)、晶圓級芯片尺度封裝(Wafer Level Chip Scale Packaging,WLCSP)以及倒裝芯片封裝(Flip Chip Packaging, FCP)陸續登上歷史舞台,它將有源區面上制有凸點電極的芯片朝下放置,與封裝基底/基板布線層直接鍵合實作冶金連線 [1–2] 。這種基於面積陣列的封裝方式不僅提高了矽片的利用率,還具有互連路徑短、訊號傳輸延時短、寄生參數小等優點。進入21世紀後,芯片中的晶體管數量仍在急劇上升,傳統二維芯片的尺寸不斷逼近摩爾定律的極限,因此人們尋求在垂直方向進行芯片整合,於是出現了3D封裝,又叫疊層芯片封裝。

不論是對於當下的面積陣列封裝還是未來的3D封裝,以金屬微凸點作為電互連和機械支撐非常普遍並將延續很長時間。然而,不同封裝層級間微凸點的尺寸跨度大、材料範圍廣,很難有一種技術能覆蓋全尺寸範圍內微凸點的制備,微凸點的制備工藝將決定該技術未來幾十年的發展。

1 金屬微凸點制備工藝

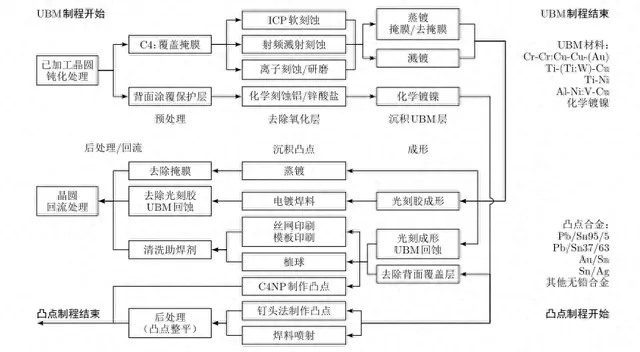

微凸點陣列的制備方法主要有2類:一類是透過專用器材將預成型精密焊球放置在基板上特定位置來形成凸點陣列,典型工藝有植球法;另一類是凸點陣列直接制備法,主要有釘頭凸點法、絲網印刷法、蒸鍍法、電鍍法(化學鍍法)、可控塌陷芯片連線新工藝(Controlled Collapse Chip Connection New Process,C4NP)以及噴射法。如圖1所示,凸點工藝主要包括凸點下金屬層(Under Bump Metallization, UBM)的制備以及凸點的制備,涵蓋了不同微凸點的制備方法。

1.1 植球法

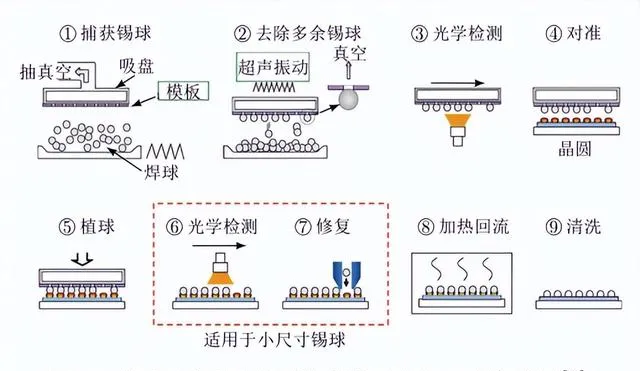

有多種植球法,其中一種是將帶有微孔陣列的吸盤置於容器上方,透過振動容器使焊球跳動,從而使其吸附於小孔之上(為去除多余焊球,可采用超聲振動工藝);隨後透過光學手段來檢測吸孔與焊球位置的準確性,緊接著將吸盤與晶圓/基板焊盤對齊,緩慢降低吸盤,使焊球置於焊盤之上,去真空釋放焊球,使吸盤與焊球分離;最後對晶圓/基板進行加熱回流形成焊錫凸點。其工藝流程如圖2所示。該方法簡單快捷,生產效率高,可靈活套用。與電鍍法相比,其成本較低且無化學汙染 [4] ,但也存在以下不足:1)對焊球的一致性要求較高,否則容易出現卡球、丟球或漏球現象;2)對助焊劑及回流溫度設定的依賴度較高,助焊劑揮發產生的氣流擾動容易使焊球位置偏移,不當的回流溫度容易造成凸點連焊;3)較難套用於細節距產品,因為難以塗布助焊劑和拾取極小的焊球;4)不適用於多尺寸焊盤的情況,如果將大小相同的焊球置於不同尺寸的焊盤上,就會降低焊錫凸點高度的共面性 [5] 。

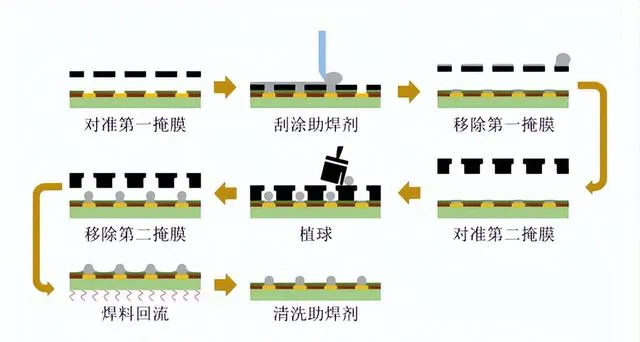

另一種是先利用第一漏印掩膜在基板焊盤上塗刷黏性助焊劑,隨後在第二漏印掩膜上均勻散布直徑相同的焊球,掩膜通孔與基板焊盤對齊,緊接著采用擠壓刷將焊球壓入掩膜通孔中,從而使焊球黏附於塗有助焊劑的焊盤上,完成植球後移除第二漏印掩膜,最後加熱回流,使焊球熔化形成凸點。其工藝流程見圖3。

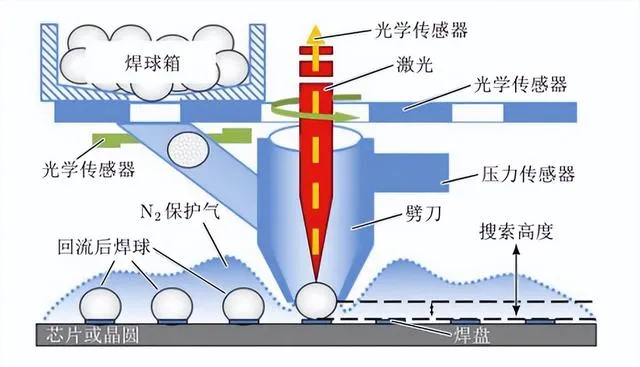

德國Pactech公司提出的激光植球技術可一步實作植球與回流工藝,其原理如圖4所示。在氮氣氣氛下利用激光束將焊球熔化在焊盤上形成凸點。該方法可用於晶圓或芯片焊盤上焊料凸點的制備,靈活性強 [7] 。由於激光局部加熱產生的熱影響區小,因此可以避免周圍元件的損傷,減少植球過程中金屬化合物層的形成,有利於提高焊點質素。激光植球技術可以實作焊球直徑為 40 ~ 760 µm的可靠連線 [8] ,但文獻[9–11]指出,該技術在焊點制備過程中會出現焊球潤濕不良、焊球凹陷、局部燒蝕等缺陷,造成焊點可靠性差。

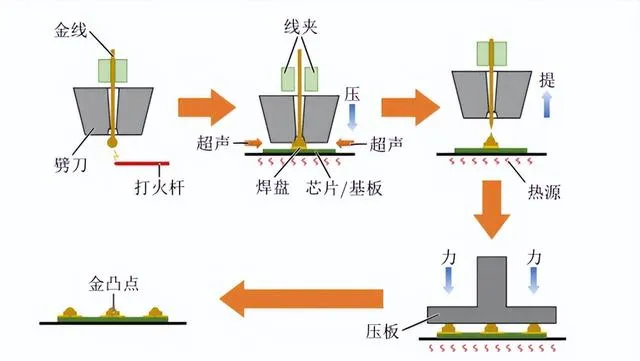

1.2 釘頭凸點法

釘頭凸點鍵合技術由Matsushita公司於1997年提出 [13] 。該方法借鑒了引線鍵合工藝 [14–15] ,在第一焊點完成後劈刀繼續向上拉伸,使金絲頸縮斷裂形成金凸點,具體工藝(圖5)如下:

1)首先利用電火花放電在金絲末端形成金球,金球尺寸可透過設定打火桿的電流、打火桿與線尾的間距以及放電時間來控制;

2)隨後在加熱、加壓和超聲的共同作用下,將金球鍵合到芯片的焊盤上;

3)當第一焊點完成後,劈刀垂直向上運動,此時線夾處於開啟狀態,送出一段尾絲;

4)線夾關閉,劈刀向上運動,金絲在拉力的作用下斷裂形成帶有尾尖的凸點;

5)當所有凸點制作完畢後,透過研磨、石英板拍平等工藝去除尾尖,使其成為高度、平整性一致的芯片凸點。

在一般情況下,為了提高倒裝焊金凸點與鋁焊盤連線的可靠性,通常會預先在鋁焊盤上濺射/蒸鍍一層UBM,而後再進行釘頭凸點制作。

釘頭凸點法只適合引腳較少、焊盤節距較大、品種多但數量相對不多的芯片封裝,具有簡便易行、方便靈活、可在單芯片上制作凸點、成本低廉等優點,但也存在凸點高度一致性較差、效率低等缺點。此外,由於金是貴金屬材料,當封裝器件的引腳數較多時,其成本要比焊料凸點高。文獻[16]嘗試使用帶有銅凸點的芯片與焊盤印刷有無鉛焊料的基板互連,意欲取代成本高昂的金凸點與導電膠鍵合的傳統互連工藝,獲得了不錯的效果,但由於銅凸點抗氧化、抗腐蝕能力差,目前很少使用。隨著鍵合工藝以及材料技術的提升,銅絲有望取代金絲成為新一代凸點鍵合材料。

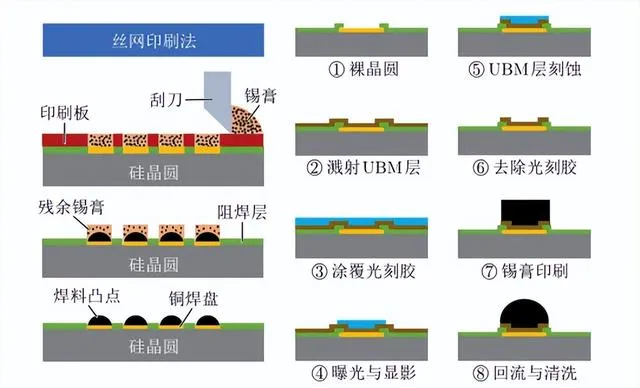

1.3 絲網印刷法

絲網印刷法是透過塗刷器和網板將錫膏塗刷在焊盤上的凸點制備技術,適用於間距為 200 ~ 400 µm的焊盤。其工藝主要包括UBM制備、錫膏絲網印刷、錫膏回流和焊盤清洗等步驟。圖6所示是目前套用較廣的低成本釬料凸點制備方法,具有效率高、成本低、適用於不同種類釬料合金的優點 [17] 。然而,該方法在節距小於 150 µm的高密度互連中面臨較大的挑戰。在細節距產品中,印刷後助焊劑容易橋接,這為回流後焊料的橋接埋下了較大隱患。在回流過程中溶劑揮發,空洞數量和凸點高度變化較明顯,降低了芯片貼裝良率。為提升貼裝良率,需采用壓印工藝保證所有焊錫凸點的共面性。此外,由於小節距焊盤掩膜的制備成本較高,因此其套用受到了一定的限制 [18] 。

隨著掩膜加工技術的提升、納米材料制備技術的日趨成熟以及印刷工藝的最佳化,絲網印刷工藝在制備節距小於 100 µm的倒裝芯片焊料凸點領域愈發成熟。文獻[19]在最佳化工藝參數的基礎上成功實作了在晶圓上制備節距為 90 ~ 100 µm的焊料微凸點。

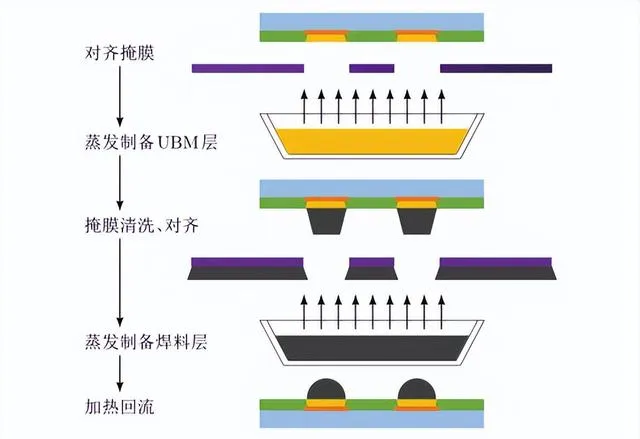

1.4 蒸鍍法

20世紀60年代IBM公司最早提出采用蒸鍍法制備凸點,主要套用於大型電腦中的多芯片模組 [17] 。在蒸鍍工藝中,先利用光掩膜制作UBM,然後將釬料蒸發到UBM上得到錐形凸點,最後對錐形凸點進行加熱回流使之成為半球狀,如圖7所示。

該方法與集成電路(Integrated Circuit, IC)工藝相相容,可充分利用現有器材且工藝成熟,但需要制作掩膜,且一種掩膜只能針對一種IC芯片。蒸鍍工藝的缺點主要表現在:1)投資高,生產效率卻不高,因此該方法僅用於要求凸點材料純度高、制備的凸點密度高或制備的凸點材料不能使用電鍍或印刷工藝等場合;2)由於大部份焊料被蒸發到掩膜和反應腔室的內壁上,因此該工藝的材料利用率極低;3)每次蒸鍍結束後,必須對附著在金屬掩膜上的焊料予以清除,而清除操作會降低掩膜質素,改變開孔尺寸,從而縮短了掩膜的壽命。UBM的制作通常使用多個蒸發器,這使得焊料成本進一步增大。蒸鍍工藝一般可接受的面陣列節距極限是 225 µm,當節距低於 200 µm時,原先采用蒸鍍工藝的公司都轉向采用電鍍工藝 [6] 。

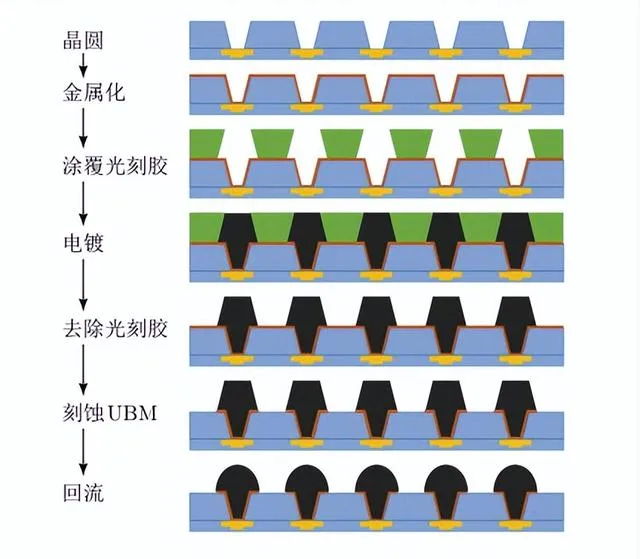

1.5 電鍍法

電鍍法是微電子封裝企業普遍采用且工藝成熟的凸點制作方法 [20] ,常用於晶圓凸點的制備。電鍍凸點所需的UBM同樣是采用蒸發/濺射的方法,但比UBM厚許多倍的凸點則采用電鍍工藝制備。電鍍法制備的凸點主要有銅柱凸點和焊料凸點2大類。銅柱凸點一般是在芯片焊盤上電鍍一定尺寸的銅柱後,再在銅柱上表面電鍍可焊性鍍層(SnPb、SnAg、Sn等),以便實作後續的互連或組裝,是當前凸點套用的主流方向。銅柱凸點被認為是可以實作窄節距凸點互連的主要材料,其特點是高度一致性好,可靠性高,節距可低至 20 µm甚至更低。焊料凸點則是直接在芯片上電鍍焊料層,經回流後形成焊料凸點。圖8為電鍍低溫釬料凸點的制作工藝流程圖。

電鍍工藝具有重復性好、一致性高的優點,同時制備工藝與IC、微機電系統(Micro-Electro-Mechanical System, MEMS)工藝相相容,可用於批次生產各類規格芯片及不同材料、不同高度的凸點,但由於資金和營運成本高,電鍍技術在小型設施中的使用受到了一定的限制。此外,三元合金(如SnAgCu)很難以一致的結果進行電鍍 [18, 21] 。

1.6 C4NP法

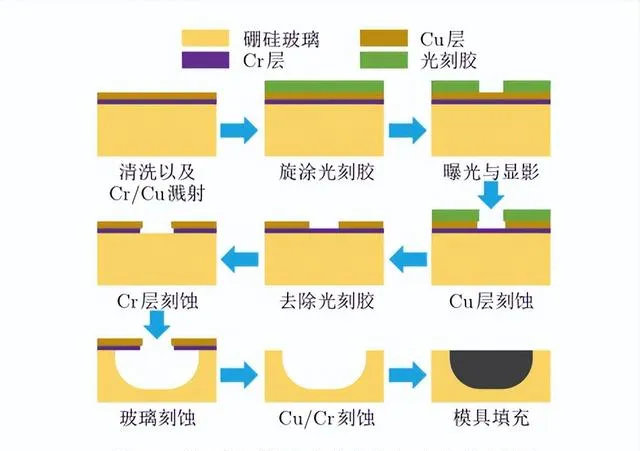

C4NP法是IBM公司研發的低成本細節距焊錫凸點制作技術,克服了現有技術的局限性,可采用多種無鉛焊料合金 [22] 。它是一種焊料轉移技術,需將熔融焊料註入預制的可重復使用的玻璃模具中,主要包括5個環節:模具制造、焊料填充、模具與晶圓對準、焊料轉印與脫模以及加熱回流。其中,模具制造是該工藝的關鍵,它包含了晶圓凸點圖形的刻蝕空腔,考慮到焊料在硼矽玻璃表面的非浸潤性,通常采用硼矽玻璃制作。圖9為模具制造及焊料填充工藝流程圖。

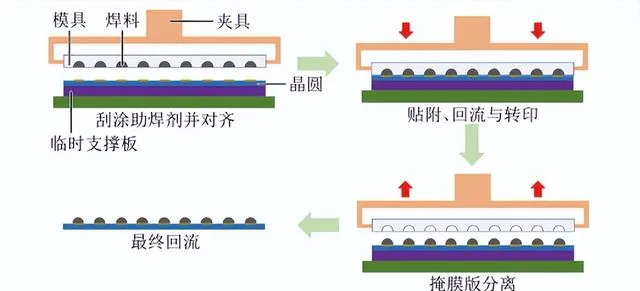

將焊料轉移至晶圓之前,需對已填充的模具進行檢查以確保較高的良率。然後在回流溫度下將填充好的模具軟接觸貼近晶圓,所有的焊料凸點將一次性全部轉移至晶圓上。該過程並無與液體流動相關的復雜問題,其工藝流程如圖10所示。

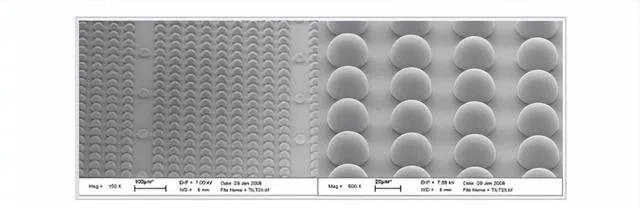

2008年IBM公司以甲酸蒸汽作為助焊劑,利用C4NP技術在直徑為 28 µm的UBM焊盤上成功實作了直徑約為 50 µm的SnAg無鉛焊料微凸點的制備 [23] ,如圖11所示。初步結果顯示:C4NP技術能輕易實作直徑在 50 µm以下的微凸點的制備,以滿足I/O密度不斷攀升的需求。

1.7 噴射法

噴射法能實作熔融焊料的高精度、超微細控制,廣泛套用於電子封裝領域球柵陣列錫球的直接噴射制備、噴射印刷電路、直接金屬快速成型、電互連線頭以及液滴鉛焊等 [24–26] 。噴射法按原理可分為連續式噴射和按需式噴射。連續式噴射透過離散層流射流來實作均勻液滴的制備,噴射的微滴具有頻率高、飛行速度快等優點,但不易對單顆微滴的飛行過程和沈積位置進行控制,故不適用於直接植球,多用於造粒 [27–28] 。按需噴射因其能精確控制液滴的體積和沈積位置,故可用於直接植球 [29] 。

噴射法按驅動方式分主要有壓電驅動式、熱泡式、導氣式、應力波驅動式、超聲振動式和電磁力驅動式 [30] 。其中,壓電驅動式是目前套用最廣且商用最成功的微液滴制備方式,但因壓電材料難以耐高溫,需要設計較復雜的冷卻系統和隔熱裝置;導氣式中的氣動膜片式解決了噴射閥不耐高溫且可噴射材料熔點受限等問題,但存在頻率較低、雜訊較大的弊端 [31–32] ;應力波驅動式能獲得比噴嘴直徑更小的液滴,液滴直徑約為噴嘴直徑的0.6倍,可大大降低噴嘴的加工難度與成本 [33] ,但存在噴射微滴定位精度差且伴有雜訊的缺點;電磁力驅動式被認為是極具潛力的驅動方式,最早套用於微泵中導電流體的驅動 [34] ,具有結構簡單、響應快、不依賴外部氣源等優點,但噴射材料必須為導體,且在噴射較高熔點材料時,需做好閥體與永磁鐵的隔熱,因較高的溫度會導致永磁鐵退磁。

采用噴射法在芯片/基板焊盤表面直接植球具有效率高、成本低、工藝簡單的優勢 [35–36] 。因此,利用微噴技術制造精密焊點成為面積陣列封裝領域的研究熱點 [37–38] 。然而,因存在工藝控制困難、一致性較差的不足,噴射法難以實作商業化套用 [39] 。噴射法一般采用按需噴射模式來實作熔融態低熔點焊料的沈積,文獻[40–44]也實作了鋁合金、銅等高熔點金屬的噴射打印。其最大特點是非接觸且無需掩膜,可透過調節氣壓、脈沖波形、脈寬、噴嘴尺寸等參數輕易控制液滴尺寸。此外,熔融態焊料噴射沈積於芯片/基板焊盤後與UBM直接鍵合,無需對整個芯片/基板進行較高溫度的加熱回流,有效保護了溫度敏感型電子元器件及內部集成電路。文獻[45–46]表明:焊料的多次回流將嚴重影響焊點的力學效能,而采用絲網印刷、電鍍等工藝制備金屬微凸點時,回流次數在20次以上 [6] ,這是噴射法的獨特優勢之一。

2 金屬微凸點常見材料

目前通用的凸點按照材料成分來分主要有以銅柱凸點、金凸點、鎳凸點、銦凸點等為代表的單質金屬凸點、以錫基為代表的焊料凸點、聚合物凸點等。

1)金凸點、銅柱凸點常用於小節距的高端芯片領域,具有電導率高、抗電遷移特性好的優點,通常采用電鍍或釘頭凸點方式制備。

2)鎳凸點和銦凸點通常用於特殊場合。鎳凸點常用化學鍍方式制備,銦凸點常用電鍍或蒸發薄膜的方式制備。

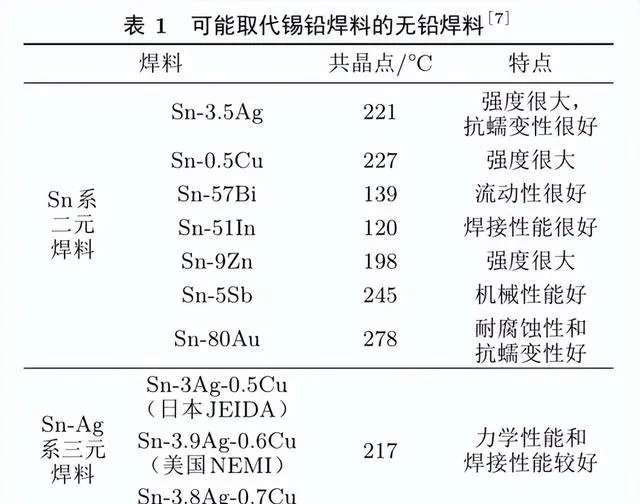

3)焊料凸點一般以錫基焊料為主,多為二元或三元及以上多元合金,其加工過程比錫鉛焊料復雜,且熔點普遍較高。表1為可能取代錫鉛焊料的無鉛焊料。

4)聚合物凸點一般由導電聚合物制備,主要用於柔性器件封裝領域。其互連工藝溫度遠低於焊料凸點的工藝溫度,通常在 140◦ C~ 170◦ C範圍內。聚合物凸點具有高度一致性好、可靠性高的優點,其器材和工藝也相對簡單,但它缺乏焊料凸點的自對中效能,位置容差較小,鍵合前必須進行高精度對準。

基於成本考慮,當節距較大(? 100 µm)時,焊料凸點仍然是基於面積陣列凸點制備的首選,而采用電鍍法制備的銅柱凸點將是高密度、窄節距微器件封裝領域當下和未來很長一段時間的主流。這是因為隨著封裝密度的提高,器件的熱流密度不斷增大 [47] ,對無鉛焊料微凸點互連器件的可靠性構成了嚴峻的挑戰。目前,最先進的銅柱凸點節距低至 40 µm,凸點尺寸約為 20 ~ 25 µm,相鄰凸點間距為 15 µm [48] 。

3 結束語

雖然目前基於無鉛焊料微凸點的制備技術比較成熟,但隨著芯片特征尺寸的不斷減小以及片上系統(System on Chip, SoC)、多芯片整合等技術的發展,I/O互連數量勢必激增,這將進一步壓縮微凸點的尺寸和節距。然而,當無鉛焊料微凸點的尺寸和節距小於一定值時,將出現一系列可靠性問題,如界面反應、熱疲勞可靠性、跌落沖擊可靠性、電遷移可靠性等。因此,在不久的將來細節距銅柱凸點將逐漸取代無鉛焊料凸點成為主流的封裝材料。此外,由於芯片三維堆疊封裝具有小尺寸、低功耗、低延遲和高頻寬等優點,能顯著提升集成電路的系統效能。因此,3D整合技術將成為評估晶圓封裝企業是否具備核心競爭力的籌碼,而與之對應的高密度矽通孔(Through Silicon Via,TSV)互連技術將備受關註。