(報告出品方:華安證券)

1封裝行業現狀與發展趨勢

1.1先進封裝屬於中道工藝,涉及部份前道工藝與裝置

半導體工藝流程包括前道晶圓制造工序和後道封裝測試工序。前道工序是晶圓制造工序。在前道工序中,晶圓經歷了氧化、塗膠、光刻、刻蝕、離子註入、物理/化學氣相沈積、拋光、晶圓檢測、清洗等一系列步驟,每一步都需要相應的半導體制造裝置。後道工序是封裝測試工序。在後道工序中,尚未切割的晶圓片進入IC封測環節,經歷磨片/背面減薄、切割、貼片、銀漿固化、引線焊接、塑封、切筋成型、FT測試,每一環節同樣需要相應的半導體封裝裝置與半導體測試裝置。最終得到芯片成品。

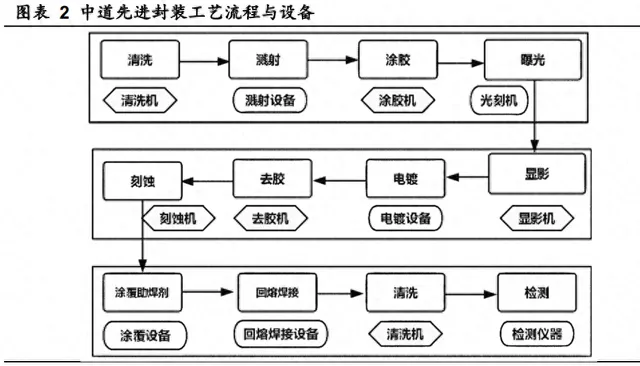

傳統封裝已不能滿足以人工智慧、高效能計算為代表的新需求,先進封裝技術應運而生,形成獨特的中道工藝。先進封裝也稱為高密度封裝,具有引腳數量較多、芯片系統較小和高整合化的特點。先進封裝屬於中道工序,包括清洗、濺射、塗膠、曝光、顯影、電鍍、去膠、刻蝕、塗覆助焊、回爐焊接、清洗、檢測等一系列步驟。

與傳統的後道封裝測試工藝不同,先進封裝的關鍵工藝需要在前道平台上完成,是前道工序的延伸。

1.2後莫耳時代,先進封裝打破「儲存墻」與「面積墻」

積體電路沿著兩條技術路線發展,分別是More Moore和More-than-Moore。MoreMoore代表持續追隨莫耳定律,致力於推動先進制程的發展。這一路線關鍵策略是透過不斷微縮互補金氧半導體(Complementary Metal-Oxide-Semiconductor,CMOS)器件的晶體管柵極尺寸,以增加芯片晶體管數量,從而提升芯片效能。目前,量產芯片的工藝制程已發展至3nm節點。全球範圍內僅有少數企業,如台積電、英特爾和三星,具備10奈米及以下節點的制造能力。與MoreMoore相對應的是More-than-Moore,這一趨勢旨在超越莫耳定律,將發展方向引向多樣化。More-than-Moore采用先進封裝技術,在一個系統內整合處理、模擬/射頻、光電、能源、傳感、生物等多種功能,從而實作了系統效能的全面提升。相對於傳統封裝方式,先進封裝具有小型化、輕薄化、高密度、低功耗和功能融合等諸多優勢,能夠提升效能、拓展功能、最佳化形態、降低成本。

推進莫耳定律成本高昂,先進封裝能夠在不縮小制程節點的背景下,僅透過改進封裝方式就能提升芯片效能。莫耳定律是指積體電路上可容納的晶體管數目,約每隔18-24個月便會增加一倍,器件效能也將提升一倍。近年來,莫耳定律的尺寸微縮趨勢放緩,先進制程已經逼近物理極限,透過邁向更先進的制程提升芯片效能的成本呈指數級增長。相比於采用45nm節點制造的250平方公釐芯片,采用1工藝節點後,每平方公釐的成本增加了1倍以上;而采用5nm工藝後,成本將增加4~5倍。與此同時,先進封裝仍處於相對高成本效益的階段。根據Semi,晶圓制造的裝置投資占比超過80%,而封裝測試的裝置投資占比不到20%。

盡管先進封裝同樣需要使用光刻、刻蝕、沈積等裝置,但相較於晶圓制造,先進封裝所需的裝置的精度要求低,其裝置價值也相對較低。此外,先進封裝技術目前正處於快速發展階段,未來有較高的改進和降本空間。

「儲存墻」制約算力效能發揮,先進封裝實作近存計算和高頻寬記憶體堆疊,提高傳輸效率。處理器的峰值算力每兩年增長約3.1倍,而動態記憶體的頻寬每兩年增長約1.4倍。記憶體的發展速度遠遠落後於處理器,兩者之間的差距達到1.7倍。

此外,日益增長的頻寬需求量也是一個重要瓶頸。數據的爆發式增長對網路資訊的傳輸速度和容量提出了更高的要求。在過去的幾十年中,序列通訊的速度從1Gb/s增長到100Gb/s,並列通訊的速度從1Tb/s增長至100Tb/s。現有計算平台的架構基於馮·諾依曼的「存算分離」,使得數據需要頻繁在儲存單元和數據單元間搬移。

為了解決「儲存墻」,業界提出了存內計算和近存計算兩種方法。存內計算是指在儲存單元中嵌入計算單元現數據的即時計算,這種計算方式可以大大減少數據搬運,降低能耗,提高計丹效率。近存計算則基於2.5D/3D先進封裝技術,實作儲存單元和計算單元的距離的縮短和多個高頻寬記憶體的堆疊,高效地傳輸數據。

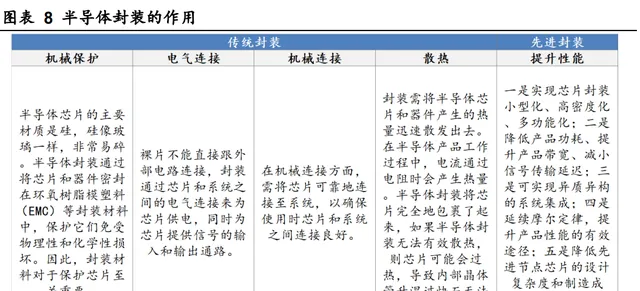

1.3封裝技術持續叠代,發展趨勢是小型化、高整合度

傳統封裝的主要作用包括機械保護、電氣連線、機械連線和散熱。1)機械保護:裸片易碎,容易受到物理性和化學性損壞。半導體封裝的主要作用是透過將芯片和器件密封在環氧樹脂模塑膠(EMC)等封裝材料中,保護它們免受物理性和化學性損壞。2)電氣連線:裸片不能直接跟外部電路連線,封裝透過芯片和系統之間的電氣連線來為芯片供電,同時為芯片提供訊號的輸入和輸出通路。3)機械連線:需將芯片可靠地連線至系統,以確保使用時芯片和系統之間連線良好。4)散熱:封裝需將半導體芯片和器件產生的熱量迅速散發出去。在半導體產品工作過程中,電流透過電阻時會產生熱量。半導體封裝將芯片完全地包裹了起來,如果半導體封裝無法有效散熱,則芯片可能會過熱,導致內部晶體管升溫過快而無法工作。

先進封裝在封裝的四大功能的基礎上,還肩負著提升芯片效能的作用。具體而言,先進封裝對芯片的提升作用包括五個方面:一是實作芯片封裝小型化、高密度化、多功能化:二是降低產品功耗、提升產品頻寬、減小訊號傳輸延遲:三是可實作異質異構的系統整合;四是延續莫耳定律,提升產品效能的有效途徑;五是降低先進節點芯片的設計復雜度和制造成本,縮短開發周期、提高產品良率。

封裝技術的發展趨勢是小型化、高整合度,可分為四個階段:1)第一階段(1970年前):直插型封裝,特點是將電子元器件直接焊接在電路板上,並透過引腳與電路板相連,以雙列直插封裝DIP(Dual In-line Package)為主;2)第二階段(1970-1990年):表面貼裝,其特點是使用更短更細的引線代替針腳或沒有引腳,將電子元件直接貼上在PCB的表面,然後透過加熱或冷凝的方式將元件固定在電路板上。

主要包括小外形封裝SOP(Small Outline Package)、J型引腳小外形封裝SOJ(Small Outline J-leaded)、無引腳芯片載體LCC(Leadless Chip Carrier)、扁平方形封裝QFP(Quad Flat Package)四大封裝技術和針柵陣列PGA(Pin Grid Array)等技術;3)第三階段(1990-2000年):面積陣列封裝,特點是用體積更小的焊球代替引線,這些球形金屬接觸點分布在芯片的表面上,形成一種類似於網格的布局。

包括BGA球柵陣列(Ball Grid Array)、CSP芯片尺寸封裝(Chip Scale Package)、倒裝芯片封裝FC(Flip-Chip)等先進封裝技術;4)第四階段(2000年至今):三維堆疊和異構整合,晶圓級封裝WLP(Wafer Level Package)、系統級封裝 SIP(System In Package)、扇出型封裝FOr(Fan-Out)、2.5D/3D封裝等先進封裝技術百花齊放。總結來看,每一代封裝技術的本質區別是芯片與電路連線方式的區別,隨著封裝技術的發展,實作了連線密度和傳輸速率不斷提高。

2典型封裝技術

2.1單芯片封裝

2.1.1倒片封裝(Flip-Chip):芯片倒置,利用凸塊連線

倒片封裝舍棄金屬引線,利用凸塊(bumping)連線。傳統的引線鍵合方法采用細金屬線進行連線,透過熱、壓力和超音波能量,將金屬引線與芯片焊盤以及基板焊盤牢固焊接,實作了芯片與基板之間的電氣互連和芯片之間的資訊傳遞。這一過程中,金屬引線在焊接的過程中起到了關鍵作用,透過引線實作了有效的電連線。

引線鍵合廣泛套用於射頻模組、儲存芯片以及微機電系統器件封裝。而倒裝封裝舍棄引線,在芯片頂側形成焊球,然後將芯片翻轉貼到對應的外部電路的基板上,利用加熱熔融的焊球實作芯片與基板焊盤結合。這種封裝技術通常被廣泛套用於高效能處理器(如CPU和GPU)、芯片組(Chipset)以及其他要求高密度互連和緊湊尺寸的積體電路封裝。

倒片封裝與引線鍵合在工藝的不同之處在於:1)倒片封裝將芯片倒置,芯片正面倒扣在基板上;2)倒片封裝舍棄金屬引線,利用凸塊連線,需要進行凸塊鍵合。

與傳統的引線鍵合相比,倒裝芯片具備眾多優勢:1)更高的連線密度:傳統的引線鍵合方法只有外部邊緣用於連線,而倒裝封裝可以充分利用整個芯片表面區域進行互聯。倒裝芯片面陣列凸點能夠提供更多的輸入輸出管腳,實作更高的傳輸速度和更低的延遲時間,適用於高功率積體電路封裝。2)更短的互聯距離:倒裝芯片之間的電氣連線不再依賴於傳統的引線,而是透過焊點直接接觸,減少了訊號傳輸時的電阻、電感,降低訊號延遲。3)更小的封裝尺寸:倒片封裝可以實作更小的封裝尺寸,因為倒裝芯片采用並列工藝,芯片之間的連線不再依賴於引線,而是透過焊點直接接觸,減少了封裝面積和體積。4)更高的散熱效率:倒片封裝可以實作更高的散熱效率,因為倒裝芯片不采用塑封封裝,使得芯片背面可以進行有效的冷卻,提高散熱效率。5)更高的可靠性:倒片封裝可以避免引線鍵合過程中出現的引線斷裂、彎曲、錯位等問題,透過環氧填充確保了封裝的可靠性和耐久性。

倒片封裝的關鍵工藝是Bumping。凸塊是定向生長於芯片表面,與芯片焊盤直接相連或間接相連的具有金屬導電特性的凸起物,按材質可分為金凸塊、焊球凸塊、銅柱凸塊。主流的凸塊工藝均采用圓片級加工,即在整片圓片表而的所有芯片上加工制作凸塊,常用方式有蒸發方式、印刷方式和電鍍方式。焊球電鍍凸塊的工藝流程為:首先,采用濺射或其它物理氣相沈積的方式在圓片表面沈積一層Ti/Cu作為電鍍所需種子層:其次,在圓片表面旋塗一定厚度的光刻膠,並運用光刻曝光工藝形成所需要圖形;然後,圓片進入電鍍機,透過控制電鍍電流、時間等,從光刻膠開窗圖形的底部開始生長並得到一定厚度的金屬層作為UBM;最後,透過去除多余光刻膠、UBMEtching及回流工藝實作電鍍凸塊制作。

2.1.2扇入型/扇出型封裝(Fan-In/Fan-Out):在晶圓上進行整體封裝,成本更低

晶圓級封裝(Wafer-Level Packaging,WLP)是一種直接在晶圓上完成封裝的技術。晶圓級封裝與傳統封裝的區別在於,傳統封裝先將成品晶圓切割成單個芯片再封裝;晶圓級封裝在芯片還在晶圓上時就進行整體封裝,封裝完成再進行切割分片。晶圓級封裝具備以下優點:1)成本更低:晶圓級封裝的成本相對較低,因為批次性處理方式使得成品晶圓能夠一次性全部封裝。2)體積更小:晶圓級封裝把整個芯片作為一個整體進行封裝,此外,晶圓級封裝通常采用無引腳或極少引腳的形式,進一步減小封裝體積。

晶園級封裝可分為兩大型別:扇入型 WLCSP(Fan-In Wafer Level Chip ScalePackage,Fan-In WLCSP)和扇出型WLCSP(Fan-Out Wafer Level Chip ScalePackage,Fan-Out WLCSP)。在扇入型WLCSP中,封裝尺寸與芯片本身尺寸相同,封裝布線、絕緣層和錫球直接位於晶圓頂部。扇出型WLCSP在封裝後的尺寸大於芯片本身尺寸,是指先對晶圓進行切割再封裝,切割好的芯片排列在載體上,芯片與芯片之間的空隙用環氧樹脂模塑膠填充,重塑成晶圓。然後,這些晶圓將從載體中取出,進行晶圓級處理,並被切割成扇出型WLCSP單元。

扇入型WLCSP具備如下優點:1)尺寸最小化:扇入型封裝實作了尺寸的最小化,最終的二維平面尺寸與芯片尺寸相同;2)工藝成本低:無需基板和導線等封裝材料,因為錫球直接固定在芯片上:3)生產效率高:封裝工藝在晶圓上一次性完成。但扇入型WLCSP也存在一些局限。由於采用矽芯片作為封裝外殼,扇入型封裝的物理和化學防護效能相對較弱。在封裝尺寸上,如果封裝錫球的陳列尺寸大於芯片尺寸,將無法進行封裝。此外,如果晶圓上的芯片數量較少或生產良率較低,則扇入型WLCSP的封裝成本要高於傳統封裝。扇入型封裝常用於低I/O數量(一般小於400)和較小裸片尺寸的工藝中。

扇出型WLCSP是對扇入型封裝的改進,具備如下優點:1)提高I/O數量:扇入型的封裝錫球均位於芯片表面,而肩出型的封裝錫球可以延伸至芯片以外。2)防護效能更強:扇出型封裝受填充的環氧樹脂模塑膠保護。

WLP工藝流程的關鍵工藝為重新布線(RDL)。首先,塗覆第一層聚合物薄膜,以加強芯片的鈍化層,起到應力緩沖的作用。聚合物種類有光敏聚酰亞胺(Pl)、苯並環丁烯(BCB)、聚苯並惡唑(PBO)。其次,重布線層(RDL),對芯片的鋁/鋼焊區位置重新布局,使新焊區滿足對焊料球最小間距的要求,並使新焊區按照陣列排布。光刻膠作為選擇性電鍍的樣版以規劃RDL的路線圖形,濕法蝕刻去除光刻膠和濺射層。然後,塗覆第二層聚合物薄膜,使圓片表面平坦化並保護RDL層。在第二層聚合物薄膜光刻出新焊區位置。隨後,凸點下金屬層(UBM),采用和RDL一樣的工藝流程制作。最後,為植球步驟,焊膏和焊料球透過掩膜板進行準確定位,將焊料球放置於UBM上,放入回流爐中,焊料經回流融化與UBM形成良好的浸潤結合,達到良好的焊接效果。

2.2多芯片封裝

2.2.12.5D/3D封裝:多層芯片堆疊,AI驅動下HBM需求大增,CoWoS產能成為算力關鍵卡口

2.5D封裝和3D封裝的區別在於是否有矽中階層(Si lnterposer)。在2.5D封裝中,所有芯片和被動元器件均在基板平面上方,至少有部份芯片和被動元器件安裝在中介層上,中介層通常作為一個載體,承載著各種電路元件和介面。而3D封裝舍棄中介層,直接在芯片上打孔和布線,電氣連線上下層芯片。所有芯片和被動元器件器件均位於基板平面上方,芯片堆疊在一起,在基板平面的上方有穿過芯片的矽通孔(TSV),在基板平面的下方有基板的布線和過孔。

根據TSV被制作的時間順序,有3種型別的TSV工藝。分為先通孔工藝(ViaFirst)、中通孔工藝(Via Middle)和後通孔工藝(Via Last),分別指TSV制作在晶圓制作工藝中的前、中或後段。

Via First是指在器件(如MOSFET器件)結構制造之前,先進行TSV結構的通孔刻蝕,孔內沈積高溫電介質(熱氧沈積或化學氣相沈積),然後填充摻雜的多晶矽。多余的多晶矽透過CMP去除。

Via Middle常常指在形成器件之後但在制造疊層之前制造的通孔工藝。在有源器件制程之後形成TSV結構,然後內部沈積電介質。澱積阻擋層鈦金屬和鋼種子層,然後電鍍鋼填充通孔,或透過化學氣相沈積鎢金屬填充通孔。

Via Last包括兩種工藝。正面後通孔工藝是在Back End of Line(BEOL)工藝處理結束後,從晶圓正面形成通孔的一種制造工藝。從概念上講,在晶圓上制造的後通孔工藝與中通孔工藝相似,但是對工藝溫度有進一步的限制(必須小於400℃)。

背面後通孔工藝是在BEDL工藝處理結束後,從晶圓背面進行通孔結構的一種制造工藝。首先使用粘合劑將兩個器件晶圓以面對面方式粘合,接下來,將頂部晶圓減薄,將TSV結構刻蝕至頂部晶圓和底部晶圓上的焊盤,孔內沈積電介質,最後,將金屬沈積到TSV結構中並進行表面金屬層再布線。

HBM使用2.5D/3D封裝技術打破「記憶體墻」制約,成為AI及高效能計算需求下的主流方案。高頻寬記憶體(High Bandwidth Memory,HBM)透過邏輯芯片和多層的DRAM堆疊來實作高速數據傳輸,突破了頻寬瓶頸,成為Al訓練芯片的首選。第一代HBM的架構由4層DRAM和邏輯芯片堆疊在一起,每層之間透過TSV和微凸點連線。每個HBM有8個通道,每個通道有128個I/O,因此每個HBM有1024個I/O,即合計1024個TSV位於HBM的中間區域。記憶體和處理器透過無源轉接板上的再布線層(RDL)將HBM邏輯芯片的埠實體層(Port PhysicalLayer,PHY)與處理器的PHY相連。HBM的效能較傳統GDDR5更具優勢,GDDR5的頻寬最高可達32GB/s,而HBM1、HBM2和HBM2的頻寬分別達到了128GB/s、307GB/s和819GB/s。其中,HBM內部的DRAM堆疊屬於3D封裝,而HBM與芯片其他部份合封於矽中介層大屬於2.5D封裝。

HBM的頻寬提升源於堆疊式封裝帶來的高位寬以及l/O速率的提升。1)位寬:HBM的位寬是GDDR5的32倍。視訊記憶體頻寬是指顯示芯片與視訊記憶體之間的數據傳輸速率,頻寬的計算公式為:視訊記憶體頻寬(GB/s)=視訊記憶體實際頻率(MHz)×視訊記憶體數據倍率×視訊記憶體等效位寬(bit)/8。GDDR5的頻率可達1750MHz,采用4倍速率機制,其等效頻率為7000MHz,但GDDR5內部I/O位寬僅32bit:相比之下,HBM的頻率為500MHz,采用2倍速率機制,等效頻率為1000MHz,但HBM內部I/O位寬高達1024bit,將頻寬提升至128GB/s。HBM之所以能實作32倍於GDDR5的I/O位寬,是因為它采用了堆疊式設計,透過TSV堆疊方式將DRAM裸片垂直堆疊放置,從而實作在相同底面積上布置了數倍的DRAM顆粒,以達到更高的I/O數量。2)1/O速率:在數值上,I視訊記憶體速率和視訊記憶體頻率是相等的,使頻寬計算公式簡化為:視訊記憶體頻寬(GB/s)=視訊記憶體數據速率(Gbps)×視訊記憶體等效位寬(bit)/8。這是因為視訊記憶體速率表示每秒傳輸的數據位數,單位為bps(bits per second),即bit·s-1。視訊記憶體頻率以MHz為單位,頻率單位赫茲的本質就是s-1,描述了單位時間內完成周期性變化的次數。

因此,在數值上,視訊記憶體速率和視訊記憶體頻率是相等的。根據JEDEC固態技術協會釋出的HBM3標準,HBM3定義高達6.4Gb/s的數據速率,堆疊中的DRAM芯片數量(四到十六個)及其具體容量(每堆疊4GB到64GB)不等,計算得到初始HBM3堆疊可提供每堆疊819GB/s的傳輸頻寬。

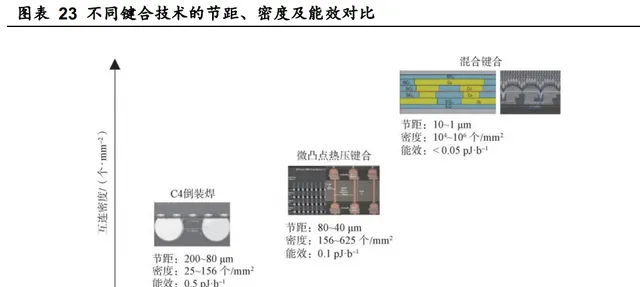

HBM堆疊層數增加對芯片間鍵合技術提出更高的要求,關鍵改進是使用混合鍵合替代原來的微凸點鍵合。混合鍵合是一種實作介質層與介質層、金屬與金屬界面無縫隙鍵合的技術,芯片鍵合界面由介質層(通常為SiO2)和金屬(通常為Cu)組成。SiO2介質層為整合單元提供機械支撐與電氣隔離,Cu-Cu鍵合提供芯片間的垂直電氣互連。對於Cu和SiO2混合鍵合結構,首先要對鍵合表面進行等離子或快速原子束表面啟用處理,之後進行直接鍵合,最後進行退火處理。退火在增強SiO2-SiO2鍵合強度的同時,也促進了Cu晶粒的生長和擴散以實作Cu-Cu鍵合。海士計劃將混合鍵合技術套用於下一代HBM4產品,混合鍵合技術可以大幅縮小電極尺寸,從而實作更高的l/O密度,同時可以顯著縮小芯片之間的間隙,減少產品厚度。

HBM的高密度連線和短互聯間距,要求台積電的CoWoS封裝技術。CoWoS是台積電於2012年研發的一種2.5D整合封裝技術,可分為CoW和oS兩步,CoW(chip on wafer)是將計算核心、I/O die、HBM等芯片封裝在矽中介層上:然後再把 CoW芯片整體封裝在基板(Substrate)上,即 oS(on substrate)環節。CoWoS可以節省空間,實作HBM所需的高互聯密度和短距離連線;還能將不同制程的芯片封裝在一起,在滿足Al、GPU等加速運算的需求的同時控制成本。目前所有先進的Al計算芯片都使用HBM,而幾乎所有HBM都封裝在CoWoS上。

根據中介層材料的不同,CoWoS有三種變體:CoWoS-S(中介層是Si襯底)、CoWoS-R(中介層由RDL構成)和CoWoS-L(中介層由Chiplet和RDL組成),其中CoWoS-S為量產主要配置。CoWoS-S利用矽片作為橋梁,芯片互聯密度最高;出於成本的考慮,CoWoS-R采用有機轉接板,但也導致芯片互聯密度較低:CoWoS-L將小矽橋安裝在有機轉接板中,僅在芯片連結部份使用矽片,實作鄰近芯片邊緣的高密度連線,生產成本和效能介於CoWoS-R和CoWoS-S之間。

2024年,CoWoS預計為台積電帶來70億美元營收。Al需求驅動下,CoWoS在台積電營收的比重逐漸上升。根據Information Network估計,2022/2023/2024年CoWoS收入占台積電營收的比例將分別達到7.00%/7.49%/8.21%。以台積電2024年全年營收指引852.37億美元估算,Al將帶來約69.94億美元的CoWoS營收,較2023年同比增長34.69%。

CoWoS的絕大多數需求來自Al。輝達的p00、A100均由台積電代工,並使用CoWoS先進封裝。根據 Omdia,2023Q3輝達售出近50萬個A100和p00GPU,Meta和微軟是最大買家,其次是谷歌、亞馬遜、甲骨文和騰訊。得益於人工智慧和高效能計算的需求,本財年第三季度,Nvidia在數據中心硬體上獲得了145億美元的收入。龐大的需求量導致CoWoS產能供不應求。除了輝達外,AMD的最新AI GPU產品MI300也匯入台積電的CoWoS(2.5D)和SolC(3D)的技術。此外,還有一系列ASIC芯片,如英特爾的Habana Gaudi、谷歌的TPUv5e、亞馬遜的Inferentia 和 Trainium芯片等。

根據我們的測算,CoWoS封裝的單價為722.08美元/顆,2023年/2024年基於CoWoS的芯片出貨量將達到346萬顆/693萬顆,其中供給輝達的芯片分別為130萬顆/433萬顆。按照12英寸晶圓面積70695mm2和p00、A100、EpicGenoa、M300四種Al芯片平均面積980mm2,測算得到每張晶圓上芯片數約72顆。擔圯Information Network給出的2022年CoWoS月產能為8500片以及前文測算022年台積電CoWoS收入,得到單顆芯片CoWoS封裝價格約為722.08美元。而根據DigiTimes的報道,2023年CoWoS年產能約12萬片,2024年將沖上24萬片,其中輝達將取得14.4-15萬片。由於這些芯片多在7nm和5nm節點生產,保守假設良率為40%。我們以輝達2023年和2024年分別取得4.5萬片和15萬片的產能來算,預計輝達出貨量約130萬顆和433萬顆。全體Al芯片出貨量約346萬顆和693萬顆,對應2023年/2024年CoWoS將產生25億美元/50億美元收入。

供需短缺情況將在13個月內得到緩解,非台積供應鏈(nonTSMC)有機會受益。台積電已於2023年第二季度開始采取行動擴產,包括將部份InFO產能從龍潭轉移至南科,以便在龍潭轉擴CoWoS產能。2023年7月25日,台積電宣布擬投資900億新台幣(約206億元人民幣)於竹科轄下銅鑼科學園區新建先進封裝廠,以加速擴產CoWoS產能,預計2026年底建廠完成,2027年開始量產。此外,台積電同時也將部份委外至其他封測廠,聯電、安靠、砂品等均提供產能支持。影響CoWoS擴產的關鍵是裝置交貨時間較長。台積電董事長劉德音在2023年9月6日出席大師論壇專題演講會時稱,CoWoS預期1年半後可100%滿足客戶需求。因此對非台積供應鏈來說,在CoW端接單的視窗期已不足13個月,加之擴產時間考慮,各封測廠商對於擴產態度與規模較為保守。

2.2.2系統級封裝(SiP):多個子芯片整合,良率更高

系統級封裝(Systemln Package,Sip)是指將多個子芯片整合在一個封裝中,從而實作一個基本完整的功能的封裝方式。傳統的莫耳定律主要關註處理器和記憶體的技術發展趨勢,而這些器件可能只占據整個系統中器件數目的10%。除此之外,系統中還包括電源、天線、過濾器、傳感器、驅動電路、轉換電路、開關、電阻和電容等。如果試圖將這些技術整合在單一芯片中,可能會導致效能不佳。因此,業界正在積極開發SiP(系統級封裝)等封裝技術,以實作更好的效能和整合。

SiP封裝技術介於SoC芯片和 chiplet封裝之間。系統級芯片SoC(Systemona Chip)將不同功能元器件整合在單個芯片,開發時間長、良率低,且各功能模組的奈米制程必須相同。系統級封裝SiP(System in a Package)將多芯片異構整合,開發時間較短、良率較高,部份可重復使用。單獨IP整合Chiplet將一類滿足特定功能的小芯粒透過die-to-die內部互聯,各功能模組的奈米制程可以不同。

SiP可以采用水平式、堆疊式或嵌入式的封裝方式。從結構上看,SiP可以分為三類,一類是2D封裝結構,其中多個芯片水平排列在基板上,這種結構的封裝面積較大,封裝效率較低,但是工藝相對簡單和穩定。另一類是堆疊封裝,其中芯片垂直疊放,這種結構可以實作高效的封裝,充分發揮SiP的技術優勢,3DSiP的實作需要多種先進的封裝工藝,如芯片堆疊(CoC)、矽通孔(TSV)等,以確保整個系統的可靠性和效能。還有一類是嵌入式封裝,需要使用埋入式基底(Embedded Subtrate)技術。

2.2.3芯粒(Chiplet):多顆小芯粒靈活組裝,支持異構整合

Chiplet將芯片劃分為小芯粒,具備靈活性和功能性優勢。Chiplet對需要實作的復雜功能進行分解,然後開發出多種具有單一特定功能的裸芯片,這些來自不同功能、不同工藝節點的裸芯片可相互進行模組化組裝,最終形成一個完整的芯片。

這種方法實作了異質整合,為芯片設計帶來了更大的靈活性和可延伸性,有效提升了產品的功能性。當前,Chiplet架構主要套用於伺服器處理器芯片、人工智慧加速芯片、通訊芯片、移動與桌面處理器芯片和晶圓級處理器芯片。

在Chiplet架構中,芯粒之間透過互連線口實作電氣連線。這些芯粒透過D2D互連線口進行電氣互連,同時透過矽轉接板和基板進行物理連線。芯粒與矽轉接板之間透過microbump互連,以支持芯粒間高速訊號的高密度互連。矽轉接板與底部基板之間則透過C4bump實作互連,用於傳遞電源和外部I/O等功能。

Chiplet具備良率、成本、異構計算優勢,適用於復雜功能的客製化需求。由於Chiplet由多顆芯粒組成,單顆芯粒的面積較小,其良率高。直接設計一整塊SoC的面積較大,可能導致較低的良率,從而帶來高昂的成本。此外,Chiplet技術支持封裝內部的異構整合,可以根據模組功能選擇芯片制程,針對特定功能模組設計專用的高效能芯片,對於其他通用芯片粒采用成熟制程。

Chiplet封裝技術也正邁向3D封裝,互聯節距持續縮小。Chiplet封裝廣泛使用各類先進封裝技術,包括2DMCM、2.3D封裝、2.5D-轉接板、2.5D-FOP、2.7D-矽橋、3D封裝-bumped、3D封裝-bumpless等。封裝結構已從2D封裝發展到3D封裝,互聯間距從12um縮短至0.5um以下,bump節距從過去的130um縮小至3um。互連頻寬逐步增加,互連品質逐步提升。

3先進封裝市場

3.1市場規模:受下遊旺盛需求拉動,先進封裝增速高於傳統封裝

Al及高效能計算需求旺盛,先進封裝景氣度高於整體封裝行業。根據JWInsights和Yole,全球先進封裝市場規模有望從2022年378億美元上升至2026年482億美元,CAGR約為6.26%。從全球封裝市場結構來看,2022年先進封裝的市場份額為47.2%。由於先進封裝市場增速超過傳統分裝市場增速,先進封裝的市場份額將持續提升,預計至2026年將達到50.2%。

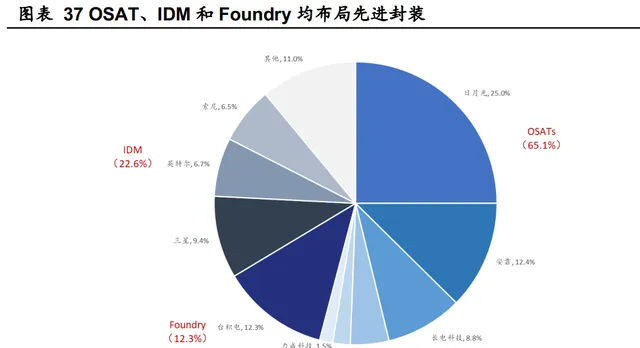

3.2競爭格局:海外IDM和Foundry掌握先進封裝前沿技術

IDM(積體電路制造商)和Foundry(晶圓代工廠)開拓高端3D封裝,而OSAT(外包封測公司)主攻中低端倒裝、晶圃級封裝。根據Yole,2022年積體電路先進封裝市場中,OSATs的市場份額為65.1%,IDM的市場份額為22.6%,Foundry的市場份額為12.3%。先進封裝頭部六位玩家市場份額超70%,包括3所外包封測公司日月光(占比25.0%)、安靠(占比12.4%)、長電科技(占比8.8%),1所晶圓代工廠台積電(占比12.3%)以及2所積體電路制造商三星(占比9.4%)、英特爾(占比6.7%)。

4重點公司分析

4.1潤欣科技:增資奇異莫耳,專註Chiplet 解決方案

潤欣科技是國內領先的IC產品和IC解決方案提供商。公司成立於2000年,自成立以來一直專註於無線通訊IC、射頻IC和傳感器件的分銷、套用設計及技術創新。目前公司主要的IC供應商有高通、思佳訊、AVX/京瓷、安世半導體、瑞聲科技、恒玄科技等,擁有美的集團、聞泰科技、大疆創新等客戶。公司劃分三個事業部:第一事業部負責工控和汽車電子客戶,以射頻、模擬、電源、分立元器件分銷業務為主;第二事業部為聲學、光學MEMS傳感器事業部,主要服務手機和TWS耳機客戶;第三事業部為AIOT事業部,負責無線連線芯片、智慧處理器芯片和模數混合芯片業務的方案設計、芯片自研和客製業務設計。2022年12月,奇異莫耳與潤欣科技簽署戰略合作框架協定,在芯片架構規劃、邏輯設計、後端設計IP整合、流片工程服務、晶圓代工廠服務等方面開展合作,進一步完善從芯片架構設計、芯粒組合到客製芯片量產交付的Chiplet產業生態。

潤欣科技在IC產品的套用設計和市場資源方面具有較強的優勢,與奇異莫耳在 Chiplet解決方案方面的優勢形成互補。奇異莫耳是一家專註於Chiplet互聯芯粒產品研發及系統級解決方案服務提供商,成立於2021年初,是國內首批專註於2.5D及3D IC Chiplet產品及服務的公司,基於下一代計算體系架構,提供全球領先的Chiplet高效能通用芯粒及解決方案。客戶只需自研部份核心芯粒,復用其他通用單元進行設計組合,即可快速形成所需專屬高效能芯片,降低研發成本和設計周期。同時,透過Chiplet 超高速互連形成超大規模系統級芯片(M-SOC),持續提升芯片效能,克服莫耳定律挑戰。目前,奇異莫耳的產品包含高效能互聯底座Basedie、高速互聯IO Die、Die2DielP、Chiplet軟體設計平台等,涵蓋了高算力芯片客戶所需的高速互聯介面、分布式近存及高效電源網路等功能。公司核心管理團隊來自全球半導體巨頭公司,團隊過往具有超過50億美金業務管理及市場行銷成功經驗,及超過10+高效能Chiplet量產計畫經驗。2023年11月,潤欣科技擬透過受讓奇異莫耳的股東奇摩兆京的部份財產份額而間接持有奇異莫耳2.88%的股權權益,雙方將基於各自的客戶和技術優勢,持續打造端到端客製化的Chiplet芯片設計服務平台,提供包含ASIC、演算法設計、Chiplet晶粒封測和芯片交付,並為客戶提供多樣化的IP、功能芯粒選擇和異構設計服務。

4.2通富微電:封測行業全球第四,提供國內最完善的Chiplet封裝解決方案

通富微電是一家國內領先、世界先進的積體電路封裝測試服務提供商。專註於為全球客戶提供從設計仿真到封裝測試的一站式解決方案。公司的產品、技術、服務覆蓋了人工智慧、高效能計算、大數據儲存、顯示驅動、5G等網路通訊、資訊終端、消費終端、物聯網、汽車電子、工業控制等多個領域。公司是AMD最大的封裝測試供應商,占其訂單總數的80%以上,收購AMD蘇州及AMD檳城各85%股權。

憑借7nm、5nm、FCBGA、Chiplet等先進技術優勢,以及不斷強化與AMD等行業領先企業的深度合作,公司鞏固和擴大先進產品市占率,2022年在全球封測行業的市占率為6.51%,上升至全球第四。

公司構建了國內最完善的Chiplet封裝解決方案,7nm產品已大規模量產,5nm產品已完成研發並逐步量產。公司透過在多芯片元件、整合扇出封裝、2.5D/3D等先進封裝技術方面的提前布局,構建八大封裝產品矩陣,並且已為AMD大規模量產Chiplet產品。FC產品方面,已完成5nm制程的FC技術產品認證,同時在多芯片MCM技術方面已確保9顆芯片的MCM封裝技術能力,並推進13顆芯片的MCM研發;在超大尺寸FCBGA-MCM高散熱技術方面,具備了Indium TIM等行業前沿材料的穩定量產能力,並成功完成了新型散熱片的開發,繼續保持公司在FCBGA封裝技術方面的行業領先地位。公司先後承擔了多項國家級計畫,並取得了豐碩的創新成栗:自建2.5D/3D產線全線通線,1+4產品及4層/8層堆疊產品研發穩步推進:基於Chip Last工藝的Fan-out技術,實作5層RDL超大尺寸封裝(65×65mm):超大多芯片FCBGAMCM技術,實作最高13顆芯片整合及100×100mm以上超大封裝。公司將持續開展以超大尺寸FO及2.5D技術為代表的先進封裝技術和產品研發,持續推進5nm、4nm、3nm新品研發,不斷強化與客戶的深度合作,滿足客戶AI算力等方面的需求。

4.3甬矽電子:Bumping通線量產,打造「Bumping+CP+FC+FT」一站式封測平台

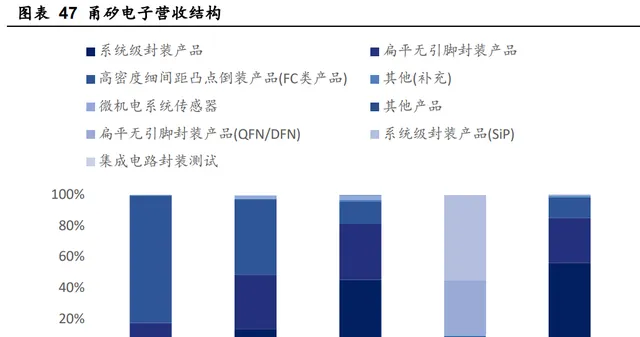

甬砂電子自成立之初即聚焦積體電路封測業務中的先進封裝領域。公司於2017年11月設立,管理團隊具有日月光、長電科技背景,全部產品均為QFN/DFN、WB-LGA、WB-BGA、Hybrid-BGA、FC-LGA等中高端先進封裝形式。下遊客戶主要為積體電路設計企業,包括恒玄科技、晶晨股份、富瀚微、聯發科、北京君正等,產品主要套用於射頻前端芯片、AP類SoC芯片、觸控芯片、WiFi芯片、藍芽芯片、MCU等物聯網芯片、電源管理芯片、計算類芯片、工業類和消費類產品等領域。目前,公司封裝產品根據技術可分為四類,包括系統級封裝產品(SiP)、扁平無引腳封裝產品(QFN/DFN)、高密度細間距凸點倒裝產品(FC類產品)、微機電系統傳感器(MEMS),2022年營收占比分別為56.28%、29.02%、13.42%、0.25%。Bumping已通線量產,初步形成「Bumping+CP+FC+FT」一站式交付能力。

在Bumping方面,公司Bumping計畫已通線量產,以12時為主,有少量客戶需要8時也會匹配其需求。公司研發的Bumping先進封裝技術,微凸塊最小高度為20um,最小凸秧直徑20um,最小間距可達34um,單晶粒(3mm*3mm)上的凸塊數量達到了3000個以上。公司研發的細線寬技術,最小線寬可達5um,最小線間距可達5um。

透過實施Bumping計畫,掌握了RDL及凸點加工能力,為公司後續開展晶圓級封裝、扇出式封裝及2.5D/3D封裝奠定了工藝基礎。在倒裝芯片FlipChip方面,FC-CSP/FC-BGA為先進的高精度倒裝芯片級封裝,具有銅柱或焊料凸塊,將芯片翻轉並連線到基板上。公司量產的FC-CSP先進封裝倒裝芯片,封裝尺寸達到17mm*17mm以上,最小凸點間距<80um,最小凸點直徑40um,單晶粒上的凸點數量在3400個以上:公司開發的高密度FC-BGA產品,單晶粒上的凸點數量達到了18000個。在射頻芯片/模組封裝方面,公司已實作5G高密度射頻模組PAMiF、PAMiD批次量產,成功開發DiFEM模組工藝。同時公司緊跟射頻模組技術的發展趨勢,布局開發更高整合密度的雙面Double side SiP(DBSiP)先進模組技術。

此外,公司在SiP、BGA、QFN、MEMS領域也擁有先進的核心技術。公司一期計畫以成熟的QFN和SiP等產品為主:二期總投資111億元,以Bumping、FC及晶圓級封裝為主,達產後具備年銷售額80億元的生產能力。

4.4其他先進封裝相關公司

長電科技:全球領先的OSAT廠商,Chiplet 4nm節點芯片封裝出貨。長電科技以10.71%的市占率在2022年全球委外封測(OSAT)榜單中排名第三,中國大陸第一。公司的先進封裝技術覆蓋全面,包括晶圓級封裝(WLP)、2.5D/3D封裝、系統級封裝(SiP)、高效能倒裝芯片封裝(FC)和引線鍵合技術等。公司研發的XDFOIChiplet高密度多維異構整合系列工藝已進入穩定量產階段,同步實作國際客戶4nm節點多芯片系統整合封裝產品出貨,最大封裝體面積約為1500mm2的系統級封裝。

華天科技:推出三維晶圓級封裝平台3DMatrix,六大生產基地分工明確。公司為專業的積體電路封裝測試代工企業,現已掌握了SiP、FC、TSV、Bumping、Fan-Out、WLP、3D等積體電路先進封裝技術,目前已構建三維晶圓級封裝平台3DMatrix,由TSV、eSiFo(Fan-out)、3D SIP三大封裝技術構成。公司有六大主要生產基地:天水基地以引線框架類產品為主,產品主要涉及驅動電路、電源管理藍芽、MCU、NORFlash等。西安基地以基板類和QFN、DFN產品為主,產品主要涉及射頻、MEMS、指紋產品、汽車電子、MCU、電源管理等。南京基地以記憶體、MEMS等積體電路產品的封裝測試為主,涵蓋引線框架類、基板類、晶圓級全系列。昆山基地為封裝晶圓級產品,主要產品包括TSV、Bumping、WLCSP、Fan-Out等。韶關基地以引線框架類封裝產品、顯視器件和顯示模組產品為主。Unisem封裝產品包括引線框架類、基板類以及晶圓級產品,主要以射頻類產品為主。

晶方科技:聚焦CIS封測,具備晶圓級芯片尺寸封裝量產能力。公司專註於傳感器領域的封裝測試業務,同時具備8英寸、12英寸晶圓級芯片尺寸封裝技術規模量產封裝線,涵蓋晶圓級到芯片級的一站式綜合封裝服務能力。封裝產品主要包括影像傳感器芯片、生物身份辨識芯片、MEMS芯片等。公司自主研發了超薄晶圓級芯片尺寸封裝技術、矽通孔封裝技術、扇出型封裝技術、系統級封裝技術及套用於汽車電子產品的封裝技術等,並引進了光學型晶圓級芯片尺寸封裝技術、空腔型晶圓級芯片尺寸封裝技術。客戶群體涵蓋SONY、豪威科技、格科微、思特威等全球知名傳感器設計企業。

(本文僅供參考,不代表我們的任何投資建議。如需使用相關資訊,請參閱報告原文。)

精選報告來源:【未來智庫】。未來智庫 - 官方網站