1. 前言

本文是專門為基於GD32 MCU開發的工程設計人員提供,主要介紹了GPIO的功能配置、內部 結構以及在不同場景使用時的註意事項,旨在幫助GD32 MCU開發者最佳化對通用型輸入輸出端 口(GPIO)的使用,正確快速的使用GD32 MCU進行產品開發。

GPIO,通用型輸入輸出埠的簡稱,可以透過軟體配置其輸出或者輸入,GD32 的 GPIO 引 腳與外部裝置連線,從而實作與外部通訊,控制以及訊號輸入的功能,是 GD32 MCU 中很常 見,使用最廣泛的模組。

每個 GPIO 引腳可以由軟體配置為輸出(推挽或開漏)、輸入、外裝置用功能或者模擬模式。 每個 GPIO 引腳都可以配置為上拉、下拉或浮空模式或無上拉/下拉。

GD32 MCU GPIO 主要特征有:

輸入/輸出方向控制;

施密特觸發器輸入功能;

每個引腳都具有弱上拉/下拉功能;

推挽/開漏輸出使能控制;

置位/復位輸出使能;

可編程觸發沿的外部中斷—使用EXTI配置寄存器;

模擬輸入/輸出配置;

備用功能輸入/輸出配置;

埠釘選配置。

對於 GD32 某些系列 MCU 的 GPIO 可能具有更多功能,如時鐘、I2C、SPI、CAN、USART、 USB、ADC、DAC 等,在進行電路板設計前應檢視該系列的數據手冊與使用者手冊,對比所使 用的 GPIO 是否滿足需求。

2. GPIO 結構

在 GD32 MCU 中,通常有兩種型別的GPIO,非 5V 耐受IO 以及 5V 耐受 IO(部份MCU沒 有 5VT引腳,如 GD32A503xx 系列),兩種型別的IO 在結構上略有區別。

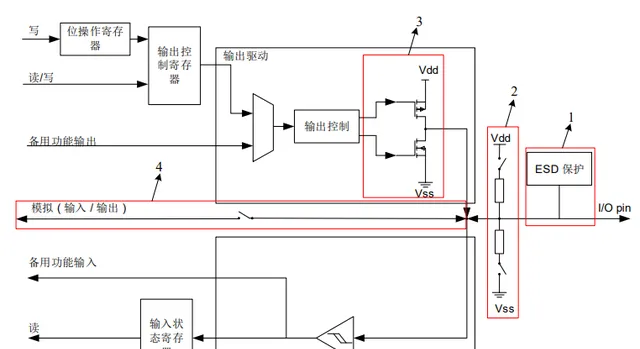

如圖 2-1. 標準 IO 基本結構圖所示為一個標準IO 口的基本結構圖:

圖 2-1. 標準 IO 基本結構圖

I/O pin 表示的芯片的 I/O pad,與外部電路相連線,其他部份電路都是芯片的內部電路。

其中框圖的上半部份表示 IO 的輸出部份電路,當IO 使用其備用功能連線內部其他外設時,也 會共用相關功率輸出部份電路。框圖的下半部份表示 IO 的輸入電路部份,作為備用功能連線 內部其他外設時,同樣也會共用輸入部份電路,如施密特觸發器。框圖的中間部份如紅框4內 的電路表示模擬輸入輸出通道,模擬通道輸出時(如 DAC 輸出)不經過功率輸出電路,輸入 時也不經過施密特輸入電路,直接將外部電路透過IO pin 與內部的模擬外設直接連線。

紅框 3 表示的是 IO 輸出時的主要功率電路,配置相關的控制寄存器,可以控制上、下兩個M OS 管導通以實作推挽輸出或者是開漏輸出。

紅框 2 表示 IO 口的內部上拉或者下拉電路,透過相關寄存器的配置可以實作輸入口的內部上 拉或者內部下拉,上拉/下拉電阻的阻值可以參考數據手冊,典型值為 40kΩ,少數引腳上下拉 電阻非 40 kΩ,如 GD32F425xx 的 PA10 引腳上下拉電阻為 10 kΩ,詳細數據可檢視數據手 冊中 GPIO characteristic 章節。

紅框 1 中表示的 ESD 保護電路。

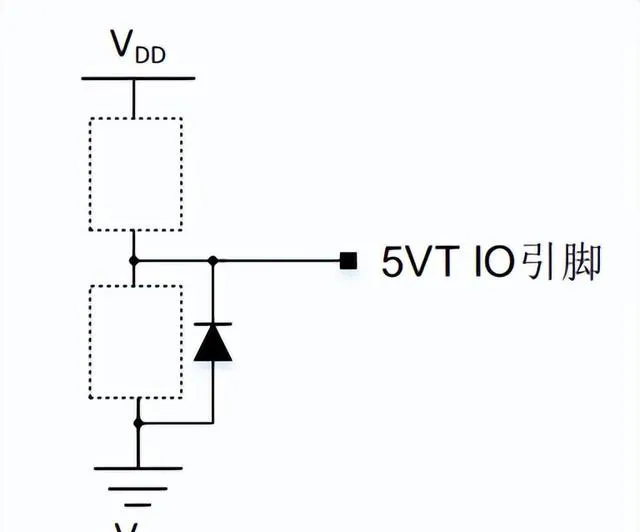

非 5VT IO 的 ESD 保護電路如圖

2-2. 非 5VT IO 引腳基本結構圖所示,ESD 保護電路在 IO 對 VDD 和 VSS分別形成兩個二極體,顯然,如果 IO 上的電壓比 VDD 的電壓大於二極體的正向 導通壓降,或者IO 上電壓比 VSS電位低,且壓差大於二極體的正精靈通電壓,則會產生從IO到 VDD,或者從 VSS到 IO 的電流。

5VT IO 的 ESD 保護電路如圖 2-3. 5VT IO 引腳基本結構圖所示,5VT IO 引腳沒有連線到電 源(VDD)的內部保護二極體。

因此,在實際使用中若存在引腳先上電,MCU 後上電的情況,優先選擇使用 5VT的引腳作為 與外部連線先上電引腳,避免由於引腳漏電造成IO 引腳拉低;若必須選擇標準IO引腳,需采 用比如三極管等隔離措施,防止引腳漏電。

圖 2-2. 非 5VT IO引腳基本結構圖

圖 2-3. 5VT IO引腳基本結構圖

圖 2-3. 5VT IO引腳基本結構圖

註意:5VT IO 與非 5VT IO 內部結構有部份區別

3. 典型套用場景與註意事項

不同型別的 IO 在使用時有一些註意事項,接下來分別從輸入與輸出兩個角度來描繪下不同類 型 IO 的典型套用場景與特性以及註意事項。

3.1. IO 輸入

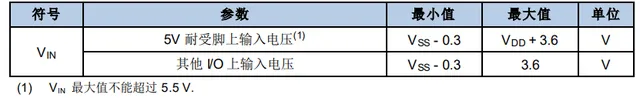

首先是 IO 口的輸入電壓範圍,輸入耐壓值表示 IO 口所能容忍的輸入電壓範圍,部份 GD32 MCU 含有 5VT IO 與非 5VT IO,5VT IO 與非 5VT IO 有著不同的特性,如使用者手冊中的表 3-1. 絕對最大額定值所示。

表 3-1. 絕對最大額定值

針對 IO 口的輸入場景,我們有幾點需要註意:

1. 對於 5VT IO,當 VDD=0 時(即 MCU 未上電時),其引腳輸入電壓不能超過 3.6V;

2. 我們需要根據 IO 口外部輸入訊號的電壓值範圍來慎重選擇 5VT IO 還是非 5VT IO,如果 輸入訊號已經大於5.5V 了,就要將訊號調理成適宜的範圍再送到 MCU 的IO 口;

3. GPIO 輸入低電平判定範圍為≤0.3 VDD ,GPIO 輸入高電平判定範圍為≥0.7VDD ;

4. 根據前面描述不同型別IO 口的典型結構,如果非 5VT IO 上的電壓比 VDD 電壓大 0.3V 以 上,則會可能使 ESD 保護電路中IO 對 VDD 的二極體導通造成漏電,尤其是在 MCU未上 電,而 IO 口就已經有電平時的情景,此時,如果選擇 5VT IO 可以有效規避從 IO 向 VDD 漏電的情況;典型的,如果IO 接入的是 I2C 匯流排,我們就需要選擇5VT引腳;

5. MCU 所有的 IO 在上電完成還未進行其他配置時,均預設工作在浮空輸入模式,其中偵錯 口為上拉或下拉模式,具體的上拉還是下拉請參照使用者手冊。因此,在一些需要產生固定 電平的場景中,如果 MCU 從待機模式復位,則需要考慮這些 IO 口的預設輸入上下拉狀 態,且在程式重新配置這些IO 的狀態之前,預設狀態不會變化;

6. 為了獲得更低的功耗水平,尤其是在睡眠模式和深度睡眠模式中,需要將未使用的 IO 配 置成模擬輸入,或者配置為浮空輸入狀態的同時外部加上下拉,或者設定為內部上拉或下 拉。需註意設定內部上拉時,外部不可再硬體下拉,避免額外功耗,同理,內部下拉時, 外部不可硬體上拉(這裏未使用的 IO 也包括在本封裝上未引出來的 IO)。對於 GD32 低 功耗 MCU 產品,在執行模式下,如前描述的設定也會獲得最好的功耗表現;

7. 5VT IO 只有在輸入模式下才可輸入最大 5.5V 電壓。當輸出模式被啟用時,5VT IO 不再可 以承受 5.5V 電壓。有關I/O 輸入電壓的詳細資訊,請參閱數據表通用操作條件表中的VIN 參數;

8. 只有在引腳上沒有啟用模擬功能時,5VT IO 才可輸入最大 5.5V 電壓。如果在5VT IO 上 啟用了一些模擬輸入功能(ADC 輸入有源,COMP 輸入,OPAMP 輸入),那麽引腳上的 最大工作電壓不能超過min(VDDA, VREFP) + 0.3 V。

3.2. IO 輸出

在 IO 輸出的場景我們也有一些要點需要註意,

1. 開漏輸出電壓與輸出帶載電流有非常顯著的關系,通常 IO 在輸出高時,如果所帶負載越 大,則輸出的高電平就會被往下拉的越低,同理,如果 IO 在輸出低時,流進 IO的電流越 大,則 IO 輸出的低電平就會被往上拉的越高;

2. 對於 MCU 中存在備份域的型號,其中有部份 IO 是工作在備份域電源中的,這些 IO的帶 載能力有限,建議這些IO 的 IO speed 參數設定為最低速度(一般為2MHz)。如 GD32F4xx 系列中的 PC13、PC14、PC15、PI8 四個引腳,不同系列驅動能力較弱的引腳不同,詳細 資訊可在該系列數據手冊中查詢;

3. GPIO 可透過電流與 IO 配置速度有關,目前所有 GD32 MCU IO 最大可透過電流均為25 mA(工作在備份域的引腳除外),GPIO 拉電流以及灌電流均不可超過 25 mA。當 GPIO 速度配置較低時,其拉電流與灌電流能力可能達不到 25 mA;

4. 部份 GD32 MCU 包含 I/O 補償單元,如E50x 系列。預設情況下,I/O 補償單元是不使用 的,當 I/O 埠輸出速度大於 50MHz 時,建議使用 I/O 補償單元對 I/O 埠進行斜率控 制,從而降低 I/O 埠雜訊對工作電源的影響;

5. IO 在高低電平轉換時過沖會隨著 IO 口速度增大而增大,可透過降低 IO 口速度來減少過 沖;

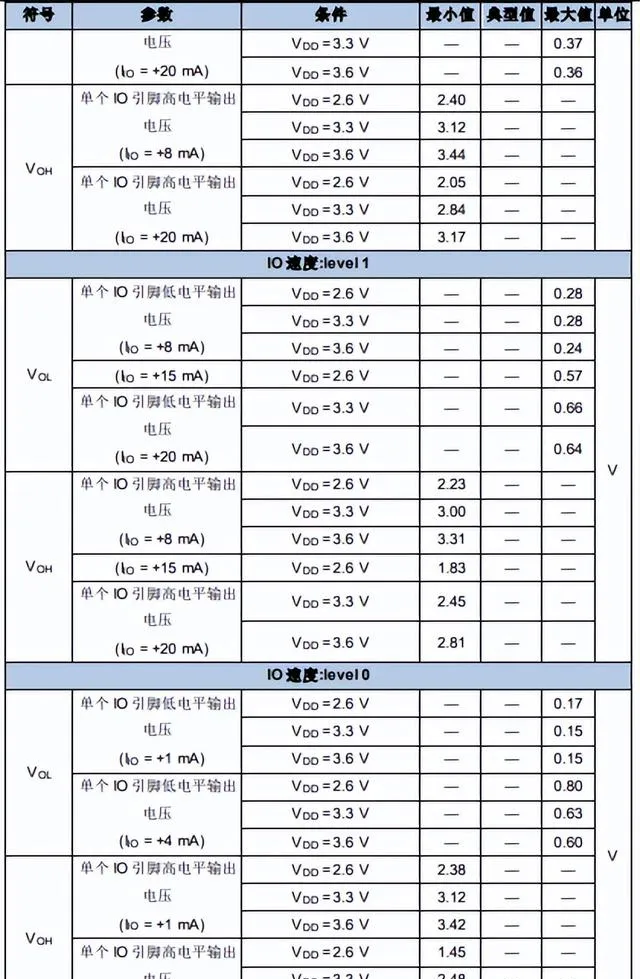

6. GPIO 輸出的高低電平並非絕對的零或者VDD,而會隨著 IO 配置的速度、VDD電壓、輸出 電流的大小而變化。如表 3-2. GD32F425xx GPIO DC 特性所示為 GD32F425xx GPIO輸 出高低電平隨這些變量變化的數據表。

3.3. 其他註意事項

為了更好的提升 GD32 MCU 在一些典型套用場景下的效能,在使用 GD32 MCU 的 GPIO時 還需註意以下事項:

1. 部份系列 GD32 MCU ADC 輸入引腳為標準 IO 引腳,需註意避免 ADC 輸入電壓超過 VDD+0.3V 的情況,否則可能由於漏電造成 ADC 采樣異常;在使用 ADC 模組時,所有 ADC 引腳均不可引入負電壓,否則將導致 ADC 采樣不準;

2. VBAT引腳允許從外部電壓源(電池或電容)為 GD32 備份域供電。當 GD32 微控制器僅透過 VBAT引腳供電時,只有在備份域裏的GPIO 才能工作。備份域的GPIO 驅動能力較弱,且 不同系列的備份域GPIO 不同,可在該系列的使用者手冊中檢視。對於沒有外部電池的套用, 建議將 VBAT引腳透過 100nF的外部陶瓷去耦電容接地後連線到 VDD 引腳上;

3. 為提高 EMC 效能,未使用的IO 口引腳建議硬體上拉或者是下拉;

4. 多組中同一標號 PIN 僅可配置一個 IO 口為外部中斷,例:PA0、PB0、PC0 僅支持三個 中的其中一個 IO 口產生外部中斷,不支持三個同為外部中斷模式;