前言

為什麽要講 ADC ,主要有2個原因:第一個原因是 選擇困惑 ,經常看到小夥伴對ADC有疑問,不知道該用 MCU內建的ADC ,還是 單獨的ADC 。第二個原因是ADC是我們在 開發時用到最多的外設功能之一 了,因為世界是模擬的,越來越多的計畫需要測量模擬訊號,根據這些訊號再去分析、計算等操作。所以如果選一個外設來講的話,那一定是ADC。

既然是芯片引腳解讀系列,就來看看MCU內部整合ADC的情況,還是以ST的MCU為例,像 STM32F412中整合的是1個16通道的12位元 , 2.4MSPS ADC ,也有一些是 整合2個,3個ADC的 , STM32H750上就整合了3個16位元,3.6MSPS 速率的ADC ,一般來說,整合的ADC的效能強弱和本身MCU效能有很大關系。

MCU內建的ADC引腳大多是和GPIO口復用的 ,16通道就是要有16個模擬輸入訊號引腳。除了輸入引腳之外,還有專門的ADC電源和地,也是我們之前講過的VDDA和VSSA,VDDA可以透過隔離器件接到VDD,也可以單獨使用基準電源芯片供電,這個根據ADC轉換要求選擇,一般都是接到VDD。

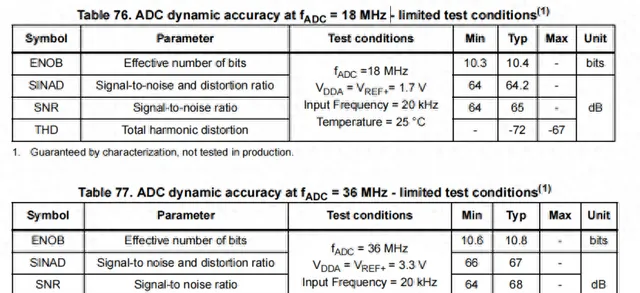

在使用內建ADC的時候,我們要註意datasheet中相關的內容,比如下面這個表裏的表示ADC動態效能參數,ENOB代表的是有效位數,SIAND訊號與雜訊失真比。

下面,就從 效能、設計難度、成本 幾個維度給大家分析下 片內ADC 和 獨立ADC 之間的區別。

效能

說實在的,內建ADC的效能提升從一些方面來說,是被框死的。ADC是模擬外設,而MCU主要是數位半導體而且速度很重要,MCU使用的混合訊號技術很難為了提高模擬功能而去犧牲數位速度。另外,ADC需要內部參考電壓,去和模擬輸入訊號的電壓電平做對比,這個參考電壓要麽來自MCU電源VDD,要麽從一個專用的引腳引入。ADC輸出精度很大程度上取決於穩定的參考電壓,因此需要在MCU內部把這個參考電源和數位邏輯分開隔離,以最大限度地減少雜訊幹擾。

雖然外部專用參考電壓引腳可以提供更好的隔離,但仍然會受到透過MCU切換的高速數位訊號的一些小幹擾,這對測量小電壓時非常重要,很可能會因為參考電壓雜訊,而遺失訊號。是不是可以使用更高的參考電壓來最大限度地減少雜訊的影響,當然可以,但要在測量低電壓時保持相同的精度,就勢必要提高分辨率,位數。這會增加芯片上 ADC 的面積,並增加 ADC在生產中的測試時間,MCU的成本無疑會增加很多。所以,內建ADC的效能提升從很多方面是被限制的。

再來看看獨立的ADC效能有多強,模擬大廠ADI的高速的ADC最多的位數可以達到32位元,采樣速率最快可以達到10GSPS。10Gsps對比MCU幾M的速率,大家想想,也就是飛機和蝸牛的速度吧。

當然,效能高並不代表一定合適。所以還需要多考慮。將ADC和MCU整合就意味著省了一顆芯片的面積,占用電路板的空間更小。而從價格上來看,帶有整合 ADC 的 MCU 的價格肯定是低於 MCU 和獨立 ADC 的組合價格,效能高的ADC芯片價格可比MCU要美麗多了。

什麽情況下選擇MCU內建的ADC?

主要看 內建ADC的精度、輸入通道數和速度等參數 是否滿足我們的設計要求。如果滿足設計要求,比如簡單的低分辨率的,就可以直接使用內建ADC,這樣既降低了硬體成本,又降低了設計復雜度。那不滿足的時候,比如一些精密的套用場合,我們就要去選擇獨立的ADC芯片,選擇的標準基本和內建ADC的選擇標準一樣,只不過外加獨立ADC的時候,還需要考慮與微控制器的數位介面, 常用的有IIC、SPI、並口等介面 。

現在MCU的效能提升,各種外設的效能也是水漲船高,很多套用,整合的ADC也都能夠勝任了。

關於ADC引腳就講這些了,下期繼續講其他引腳~

完整資料可進群免費領取!!!

嵌入式物聯網的學習之路非常漫長,不少人因為學習路線不對或者學習內容不夠專業而錯失高薪offer。不過別擔心,我為大家整理了一份150多G的學習資源,基本上涵蓋了嵌入式物聯網學習的所有內容。點選下方連結,0元領取學習資源,讓你的學習之路更加順暢!記得點贊、關註、收藏、轉發哦!

點選這裏找小助理0元領取:掃碼進群領資料