英特尔试图重回芯片制造和代工领域的前沿,而台积电定义这一前沿的举措将在今年 12 月于旧金山举行的国际电子设备会议 (IEDM) 上得到展示。

在一篇新闻中,台积电的研究人员表示,公司将在本届的IEDM公布 N2 制造工艺,这是一种标称 2nm 工艺,专为 AI、移动和高性能计算而设计。在同一场会议的下一篇论文中,英特尔工程师将提供有关 RibbonFET(英特尔为其纳米片晶体管起的名字)的扩展细节。

在 IEDM 会议上,台积电的研究人员预计将报告称,与 2022 年推出的 N3(标称 3nm)工艺相比,N2 的速度可提高 15% 或功耗降低 30%,芯片密度也可提高 15% 或更高。

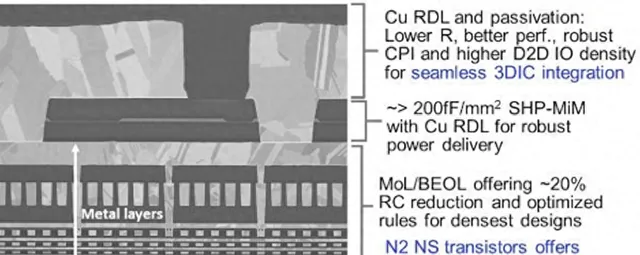

N2 互连堆栈的横截面显示铜重分布层。来源:IEDM 和 T 横截面图显示,N2 平台的 Cu 重分布层 (RDL) 和钝化层可与 3D 技术无缝集成。

台积电的 G. Yeap 等人撰写的论文 2.1 2nm 平台技术,具有节能纳米片晶体管和互连,与 3DIC 共同优化,适用于 AI、HPC 和移动 SoC 应用,还将展示具有世界纪录密度为每平方毫米 38Mbits 的 SRAM 宏。

本文还将详细介绍中段(MEOL)和后端(BEOL)互连,其特点是可扩展的铜基重分布层,可灵活放置输入/输出焊盘并降低阻挡电阻);平坦的钝化层(用于提高可靠性);以及硅通孔或 TSV(用于连接不同层的设备)。

研究人员表示,N2 平台已满足晶圆级可靠性要求和初步资格测试。预计 2025 年实现全面认证,2026 年实现量产。

英特尔

在论文 2.2【6nm 栅极长度的硅 RibbonFET CMOS】中,来自英特尔的 A. Agrawal 等人准备展示如何构建具有 6nm 栅极和 45nm 接触多晶硅间距(CPP,晶体管栅极之间的间距)的纳米片技术 (RibbonFET),并且不会降低电子迁移率。

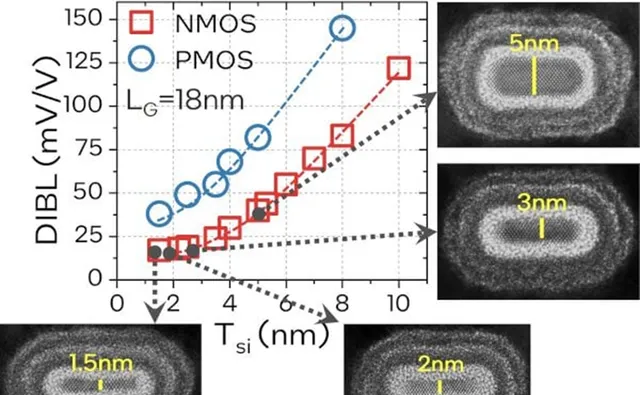

栅极长度为 18nm 时漏极诱导势垒降低 (DIBL) 与硅厚度 (Tsi) 的关系。随着 Tsi 从 10nm 缩小到 1.5nm,DIBL 降低;然而,DIBL 降低在 Tsi <4nm 时达到饱和。在相同 Tsi 下,PMOS DIBL 与 NMOS DIBL 相比有所升高。图中还显示了 1NR 晶体管的 TEM 显微照片,其 Tsi 值低至 1.5nm。来源:IEDM。

作者没有提及英特尔的具体制造工艺,但 RibbonFET 计划在 20A 工艺(即标称 20 埃或 2nm 工艺)中投入生产。英特尔似乎选择不推出任何基于 20A 的处理器产品,而是直接从 3nm 工艺转向 18A 工艺,这可能反映在作者对纳米片缩放的关注上。

研究人员将证明,在纳米片硅厚度达到 3nm 之前,电子迁移率不会降低。此后,由于表面粗糙度而导致的电子散射成为一个问题。在论文中,作者报告了 4nm 以下硅厚度的短通道控制和功函数工程如何实现以 3nm 为基准的低阈值电压。

2nm 技术竞赛

英特尔、三星和台积电正处于在其 2 纳米节点中实施背面供电技术的竞争前沿,旨在增强其在 AI 芯片市场的竞争力。这项创新技术有望通过将供电网络重新定位到硅片背面来提高芯片效率,此举旨在简化电源效率、减少干扰并提高整体性能。英特尔今年在商业化方面处于领先地位,三星电子和台积电紧随其后,准备在 2025 年进行大规模生产,业界对背面供电的变革性影响充满期待。

工程师在缩小半导体芯片上晶体管的尺寸时面临哪些挑战,背面供电技术的采用将如何重塑半导体制造和设计的格局,以及这一进步将如何影响未来移动应用处理器和人工智能芯片的发展?

一、要了解的关键事项:

英特尔引领潮流:英特尔将于今年利用其 PowerVia 解决方案将背面供电技术商业化,旨在提高芯片性能和效率。

竞争优势:背面供电技术提高了电源效率并减少了干扰,这对人工智能应用和移动处理器至关重要。

行业转变:三星和台积电也在迅速推进其背面供电技术,三星的目标是到 2025 年实现大规模生产。

重大影响:背面供电技术的采用有望改变半导体制造工艺,实现更紧凑、更高效的芯片设计,并推动整个行业的创新。

二、微型化的极限:未来设备进步的瓶颈

对微型化的不懈追求一直是电子技术进步的驱动力,使更小、更强大、更节能的设备得以诞生。然而, 随着工程师们 接近晶体管尺寸的根本极限,晶体管缩小所带来的挑战开始阻碍进一步的微型化。干扰增加、功率效率降低以及芯片正面电路和电源线空间有限,这些因素共同阻碍了 更先进设备的开发 ,引发了人们对设备微型化未来的担忧。

三、小型化中的技术挑战

随着晶体管变得越来越小,工程师面临着众多技术挑战,如果不加以解决,可能会对电子设备的性能和可扩展性产生连锁反应。材料的物理限制和 物理原理(如量子隧穿和散热)给半导体芯片的设计和制造带来了重大障碍。芯片正面电路和电源线的拥挤加剧了这些问题,导致电力输送效率降低,信号传输干扰增加。

传统的前端供电方法一直是业界的标准做法,但这种方法根本无法适应现代电子设备的复杂性。芯片前端的电源线和数据传输路径非常接近,这会导致串扰、噪声和信号干扰,从而降低电子元件的性能并增加能耗。空间的缩小还会导致发热量增加,进一步影响供电效率和 设备的整体功能。

四、设计限制和集成问题

此外,半导体芯片正面设计的限制阻碍了附加电路和电源线的集成,从而限制了电子设备的功能。随着芯片上晶体管密度的增加,安装缓冲器、驱动器和控制电路等额外组件成为一项挑战,限制了 设备的整体设计灵活性和功能性。 空间的减少也降低了提高功率效率的潜力,阻碍了低能耗电子系统的开发, 而这些系统对于未来电子设备至关重要,因为它们要努力满足日益严格的能源和碳排放标准。

五、英特尔的背面供电:半导体行业的游戏规则改变者

追求更小的芯片尺寸和更高的功率效率已成为行业巨头英特尔、三星和台积电之间竞争的关键因素。背面供电技术(将供电网络从硅片正面移至背面)的实施是这场竞争的核心,三家公司都在竞相率先将这一创新解决方案商业化。

六、背面供电面临的挑战

实现高效背面供电面临的主要挑战之一是在芯片的有限空间内集成电源和信号布线。根据英特尔最近的 PowerVia 测试,将供电与信号路径分离可显著提高单元利用率,实现 90% 以上的效率。这对于满足日益增长的 AI 和图形应用需求至关重要,因为这些应用需要高密度和高性能的芯片设计。

背面供电的优势非常显著,它不仅能提高芯片性能,还能提高电源效率并减少信号干扰。借助这项技术,芯片可以变得更小,这对于需要低能耗和紧凑设计的移动应用处理器来说是一个很大的优势。使用 背面供电还可以减少对配电层的需求,从而减少制造步骤总数并降低与半导体生产相关的成本。

六、解决互连瓶颈

英特尔的创新方法(如其 PowerVia 技术所示)还解决了互连瓶颈问题。通过将电源布线移至晶圆背面,英特尔解决了芯片设计中最紧迫的挑战之一。这不仅简化了制造过程,还改善了热管理,这对于保持高密度电路的性能和可靠性至关重要。

虽然英特尔有望凭借其 PowerVia 解决方案率先实现背面供电商业化,但三星和台积电正在迅速崛起。三星将其商业化时间表从最初计划的 2027 年提前到 2025 年,这表明该公司在背面供电技术方面的发展速度很快。有报道称,三星可能会从 1.7nm 工艺开始实施这项技术,2nm 工艺将是主要重点。然而,台积电一直对其计划保持沉默,对其开发进度保密。

七、PowerVia 增强性能

英特尔在 PowerVia 方面的进步不仅限于电源效率。采用 PowerVia 技术的测试芯片显示平台电压下降改善了 30%,频率性能提高了 6%。这些增强对于 AI 芯片的整体性能具有重要意义,因为它们确保了稳定高效的电力输送,这对于高性能计算任务至关重要。

英特尔在这一领域的发展尤其值得关注,即将推出的 Arrow Lake 台式机 CPU 将采用 英特尔 20A 节点和 PowerVia 技术。该公司计划在今年晚些时候推出首款 2nm 芯片, 这进一步 表明了其对这项创新技术的承诺。英特尔 20A 节点使用背面供电 不仅可以提高芯片性能,还可以 提高电源效率,这是业界追求降低能耗的关键因素。

此外,英特尔专注于将 PowerVia 开发与晶体管进步分离开来,这使得他们能够独立完善这项技术。这一策略确保在将 PowerVia 与英特尔的下一代 RibbonFET 晶体管(将在 20A 工艺节点中引入)集成之前对其进行优化。这种有条不紊的方法有助于降低风险并确保无缝过渡到更先进的半导体节点。

八、解耦 PowerVia 开发

英特尔、三星和台积电之间的竞争愈演愈烈,每家公司都在努力实现更小的芯片尺寸和更高的功率效率。背面供电技术的实施 是这场竞争中的重要一步,因为它可以提高芯片性能、提高功率效率并减少信号干扰。虽然英特尔将首先实现这项技术的商业化,但三星和台积电正在迅速崛起,三星正在推进其商业化时间表,而台积电则对其开发进度保密。缩小尺寸的竞争 仍在继续,背面供电技术的推出标志着半导体制造的新时代。

九、背面供电改变半导体制造

半导体行业正处于十字路口,随着英特尔、三星和台积电等芯片制造商 将重点转向 提高 2nm 技术节点的功率效率和减少干扰,背面供电技术的采用势头强劲。这种从传统正面供电系统的转变是为了应对电路设计尺寸缩小带来的日益严峻的挑战,其结果可能会改变 AI 芯片市场以及未来移动应用处理器 (AP) 和 AI 芯片的发展。

十、IEEE 认可和英特尔的领导地位

IEEE 已将背面供电确定为下一代 2nm 工艺节点的关键技术,该技术有望通过提高电源效率和性能来提供竞争优势,而这对 AI 应用至关重要。凭借其 PowerVia 技术,英特尔有望引领潮流,旨在将其集成到即将推出的 20A 节点和 Arrow Lake CPU 中。高效供电的能力将为行业树立新标准,为提高 AI 芯片的性能和效率铺平道路。

背面供电对未来移动 AP 和 AI 芯片的发展影响 巨大,该技术可实现更紧凑、更高效的设计。通过缩小芯片尺寸,背面供电可显著造福移动设备,实现更先进的 AI 应用,同时提高功率和频率效率。该技术还有望减少信号干扰和制造挑战,从而为整个行业带来更强大、更可靠的 AI 应用。

十一、芯片架构的创新与小型化

采用背面供电技术为芯片架构和制造工艺的创新开辟了新途径,为半导体技术的进一步小型化和效率提升奠定了基础。领先的芯片制造商尽早采用和改进这项技术可能会加速整个 半导体行业的进步,从而开启半导体制造的新时代。

半导体行业 处于技术创新的前沿,向背面供电技术的转变是提高电源效率、减少干扰和推动半导体制造进一步进步的重要一步。随着英特尔、三星和台积电等芯片制造商继续在这一领域取得进展,业界有望 看到 紧凑高效的设计、人工智能应用性能的提升,以及芯片架构和制造工艺创新的新机会。