本文約8,000字,建議收藏閱讀

作者 | 林Nova

出品 | 汽車電子與軟件

本文主要介紹嵌入式內核架構原理,及當前嵌入式市場主流MCU內核架構。

#01

前 言

1.1 內核簡介

電腦芯片內核架構 (Processor Core Architecture)是指構成微處理器芯片的基本設計和組織結構,它定義了處理器執行指令、處理數據和控制程式執行的方式。簡單來說,如果把大腦比作CPU,內核架構就相當於大腦內部各種中樞的組成和工作原理。不同系列的芯片根據使用場景和需求,采用不同的內核架構。

電腦內核離不開 內核指令集 ,內核指令集是電腦內核編程介面的具體形式,它將電腦內核的操作透過整合和拆分,最終組織成一套能夠實作內核控制的指令系統。

不同的內核具有不同的內核指令集,比如我們日常使用的電腦(Intel或AMD芯片),使用的就是 X86指令集 ,內核就屬於 X86架構 。常見的還有ARM架構、DSP架構和RISC-V架構。當我們想要掌握某款芯片,基於該芯片進行系統搭建時,就必須要了解該芯片的內核。

內核與指令集之間的關系是密切且復雜的,每種內核架構都有與之匹配的內核指令集,而內核與指令集之間有對應的版本匹配關系,例如,Cortex-A8和Cortex-A9內核是基於ARMv7-A指令集架構的,而Cortex-M3和Cortex-M4則是基於ARMv7-M指令集架構的。這裏的"v7-A"和"v7-M"就是指令集架構的版本,代表它們支持的指令集類別。

1.2 內核分類

電腦內核指令集按照指令類別可以分為兩種,一種是 精簡指令集(RISC,Reduced Instruction Set Computing)電腦 ,它是一種電腦處理器架構設計理念,其核心思想是將處理器的指令集設計得相對較小和簡單,以提高執行效率。RISC架構強呼叫更少、更基本的指令來完成操作,並且這些指令的執行時間相對較短。

另外一種是 復雜指令集(CISC)電腦 ,是一種電腦處理器設計模式,其主要特征是支持大量的、復雜的指令系統。CISC架構的設計理念是透過設定一些功能復雜的指令,把一些原來由軟件實作的、常用的功能改用硬件指令實作,以此來提高電腦的執行速度。這種設計使得CISC架構的處理器擁有大量且種類繁多的指令,包括基礎算術邏輯運算、數據傳輸、控制轉移、處理器狀態管理、高級數據處理以及系統級指令等。

內核的分類一般是與指令集相匹配的,畢竟是共生設計出來的,比如與精簡指令集配套的就是精簡指令集內核架構。

嵌入式領域的芯片一般都是精簡指令集內核架構,這符合嵌入式領域資源需求低,即時性要求高等特點。

#02

內核介紹

從電腦原理的角度來說,內核架構主要包括內核的運算方式、指令系統、CPU的結構和功能、中斷系統等。

2.1 內核數據類別及運算方式

每一種內核,都有其固定的參與運算的各種數據類別,以及它們在內核中的算術運算方法。

對於數據類別來說,內核的數據類別有兩種:有符號和無符號。其按照原碼、補碼、反碼的形式在記憶體中做具體實作。

|

真值 |

源碼 |

補碼 |

|

+3 |

0011 |

0011 |

|

+2 |

0010 |

0010 |

|

+1 |

0001 |

0001 |

|

0 |

0000 |

0000 |

|

-1 |

1111 |

0001 |

|

-2 |

1110 |

0010 |

|

-3 |

1101 |

0011 |

|

-4 |

1100 |

0100 |

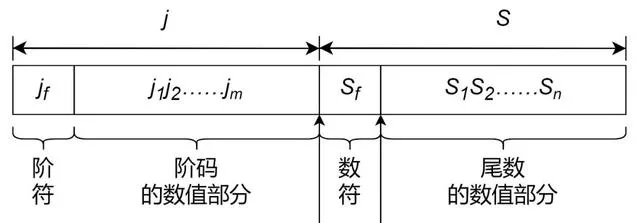

對於小數的表示,分為定點數和浮點數。定點數即小數點在固定的位置,浮點數則使用科學計數法,將數值分為4個部份,嵌入式內核一般使用浮點數表示法。

一般來說,這些數據類別在各類嵌入式系統中都是支持的,並沒有太大的差異。下圖是英飛淩TriCore 1.6.2架構中所支持的數據類別。

而在運算方式上,RISC架構下主要包括加減乘除、移位等運算,不同的內核硬件處理方式速度上表現略有不同。

2.2 指令系統

我們知道,在編寫嵌入式程式碼時,我們使用的C語言屬於高級語言;然後需要使用編譯器將其編譯成機器語言,也就是組合語言;最終燒錄到機器中,內核將其譯碼,然後真正地執行。

對於普通程式設計師來說,只需要學習C語言、C++等高級語言,一般不需要關心下層細節,因為編譯器會做隔離。

對於不同類別地內核架構,因其內部硬件機制的不同,產生了不同的機器語言,而面向使用者則需要提供配套的機器語言。人們習慣把每一條機器語言的語句稱為 機器指令 ,而又將全部機器指令的集合稱為機器的 指令系統 。

不同的內核有著截然不同的指令系統,即使同系列的如ArmV7-M與ArmV7-A之間也有些許差異。

指令格式

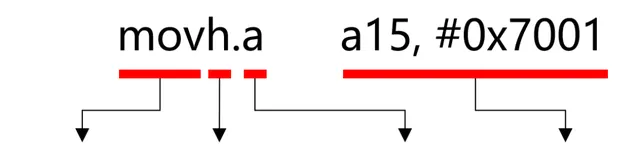

指令的一般有兩部份組成, 操作碼 和 地址碼 。

操作碼用來指明該指令所要完成的操作,如加法、減法、傳送、移位等。其位數反映了內核所能支持的操作類別數量,比如操作碼占7位,則該內核最多包含2^7=128種指令。

地址碼用來指出該指令的源運算元的地址、結果的地址以及下一條指令的地址。這裏的地址可以是記憶體的地址,也可以是寄存器的地址、棧的地址。

不同的內核機器指令字長不同,嵌入式MCU的指令字長一般是32位元,大多數內核也同時支持16位元指令,用以精簡程式碼容量。

運算元

一條完整的組譯程式碼一般包含指令和運算元,運算元的常見類別有地址、數碼、字元、邏輯數等。

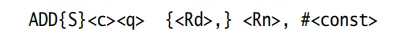

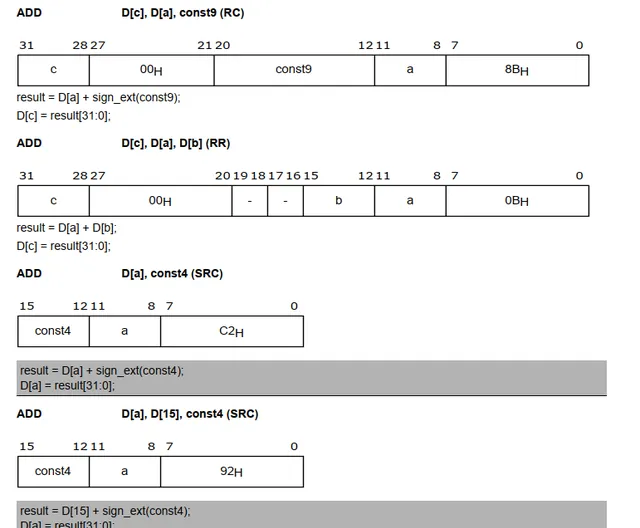

下面是ArmV7-M中一條加法指令的格式,包括一條加法指令兩個寄存器和一個立即數:

尋址方式

尋址方式是指確定本條指令的數據地址以及下一條將要執行的指令地址的方法,它與硬件結構緊密相關,而且直接指令格式和指令功能。尋址方式主要分為 指令尋址 和 數據尋址 兩種。

指令尋址比較簡單,有我們常見的程式執行完之後PC自動累加,執行下一條指令,稱為 順序尋址 ;還有一些跳轉類的指令,如Jump等稱為 跳躍尋址 。

數據尋址的方式就比較豐富了,它包括 立即尋址、直接尋址、隱含尋址、間接尋址、寄存器尋址、寄存器間接尋址、基址尋址、變址尋址、相對尋址、堆疊尋址 等模式。

如下圖中列出英飛淩TriCore的加法指令的幾種形式,有立即尋址、寄存器尋址、隱含尋址等方式。

另外除了這些常規的數據操作指令,根據不同內核的機制和特性,還存在一些具有內核特色的特殊指令,比如ARM中的數據屏障指令 DSB ,TriCore的低上下文保存指令 SVLCX 。

RISC VS CISC

RISC指令系統相對於CISC指令系統,因為采用了更少的指令,因此內核的芯片電路設計上要節省更多的面積,這些面積能夠供其他功能使用,如提供更多的寄存器。

另外由於指令種類少、通用寄存器多、流水線設計友好等特性,RISC一般運算速度要高於CISC。

2.3 CPU結構與功能

CPU結構

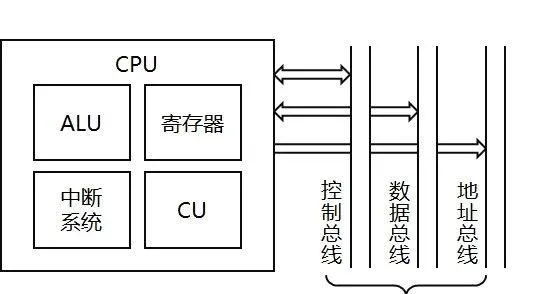

CPU實質包含運算器和控制器兩大部份。如下圖所示,一般電腦內核的最小系統中包括邏輯運算單元ALU、寄存器、中斷系統、控制部件CU。

寄存器

寄存器是電腦芯片中速度最快、容量最小、位價最貴的記憶體,它們設在CPU內部,用於CPU各種控制和運算。寄存器大致可分為兩類:一類屬於普通使用者寄存器,用於常規計算使用,包括通用寄存器、數據寄存器、地址寄存器等;另一類是控制和狀態寄存器,用於控制CPU的狀態等,一般由作業系統等特權程式使用。

一般我們說某款芯片是多少位,如32位元等,是說這款芯片的數據處理寬度,通常也是寄存器寬度。嵌入式領域中的芯片寄存器寬度一般是32位元。

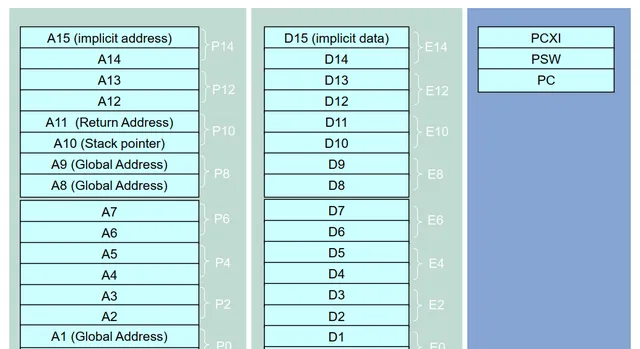

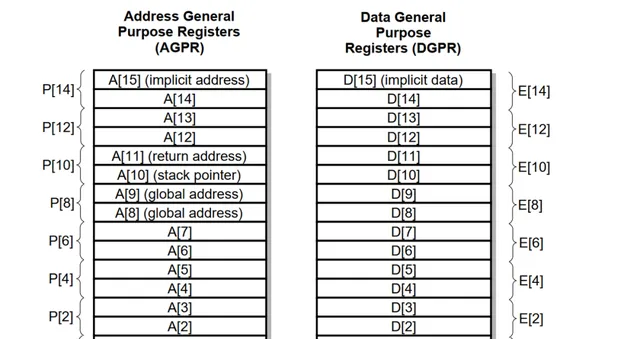

不同的內核,根據其結構設計不同,有不同的寄存器結構。比如下圖中英飛淩的TriCore內核寄存器,除了常規的16個數據寄存器以外,還增加了16個地址寄存器,其中包括棧指標寄存器和返回地址寄存器,系統寄存器中則有專用其上下文系統使用的PCXI寄存器。

指令周期和指令流水

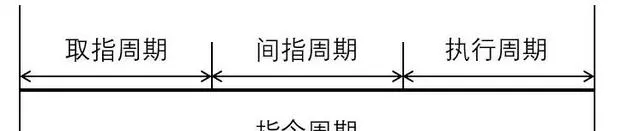

CPU取出一條指令並執行所需的全部時間稱為指令周期。一般情況下,一個指令周期包含多個操作流程,比如當遇到間接尋址的指令時,需要經過以此間接尋址,因此指令執行分為三部份。

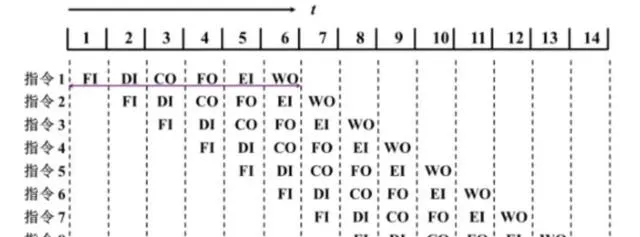

CPU中機器指令的每個操作流程一般對應一個硬件單元,稱為 指令部件 ,這些硬件單元在程式中接力完成指令執行,就像是 流水線 一樣。假設我們將指令的流程分為6步:取值(FI)、指令譯碼(DI)、計算運算元地址(CO)、取運算元(FO)、執行指令(EI)、寫運算元(WO),如下圖中,當時間進行到第2列時,指令1已經完成了FI進入到DI,此時FI指令部件能夠對下一條指令進行取值,實作並列,而在同一時刻,最多有6條指令在同時處理(下圖同一列),這種技術稱為 指令流水 ,而根據流水部件數量,圖中的流水稱為 六級流水 。

當然,程式的執行有前後依賴的,指令流水能做到多流暢,除了取決於芯片廠商的流水線設計能力,還取決於程式碼邏輯。通常影響流水的因素有結構相關、數據相關、控制相關等。

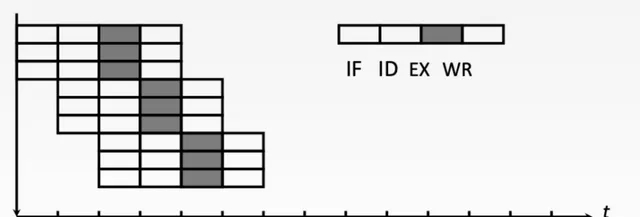

流水線多發

一定程度來說,流水線技術從空間上加速了程式的執行。而為了進一步發展,還可以進行流水線多發技術,在一個時鐘周期內產生更多條指令的結果,簡單來說,就是增設多條流水線。最常見的就是 超純量技術、超流水線技術、超長指令字技術 。

下圖中展示的就是多條流水並列的超純量技術,可以看到有四級三條流水並行,最多12條指令同時執行。但是同樣受限於程式執行邏輯及順序,其對編譯最佳化的依賴較強。

2.4 中斷系統

不管是嵌入式領域,還是其他電腦,程式在執行過程中要與外界透過I/O進行互動,因此會接收到外界的各種訊號,以及定時器事件、程式異常等特殊事件。對於這些特殊事件需要進行及時響應,也就是暫停當前的程式立即前往指定的程式碼處處理對應的邏輯,該流程稱為 中斷 。廣義的中斷包括中斷和異常。

因此對於各種內核架構,都需要設計出中斷系統,以應對各種需要的中斷場景。

中斷因素

引起中斷的因素有很多,如人為設定的軟件中斷,數據溢位、空指標等異常類中斷,還有硬件故障類中斷。另外當我們設定完硬件之後,硬件一旦完成操作或者就緒,就會發出中斷如ADC中斷、SPI中斷等。

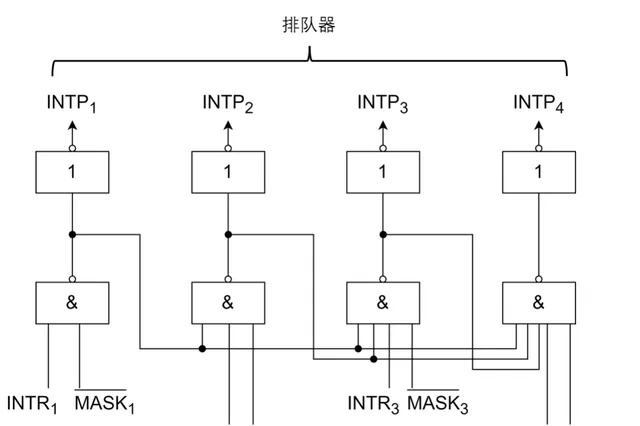

中斷響應

在內核執行每一條指令之後,會去查詢中斷狀態,判斷是否有中斷產生,這也是中斷響應的最小時間顆粒度。當多個中斷同時產生時,在嵌入式MCU領域,一般需要根據優先級進行排序。並且當高優先級中斷執行時,低優先級中斷不能夠進行打斷,下圖是帶有遮蔽和排隊功能的中斷系統邏輯電路示意圖。

中斷處理

中斷處理流程一般包括保護現場、處理中斷服務程式、恢復現場等流程。對於不同內核有著不同的處理機制,有的廠商還會再為了提供即時性做一些特殊設計,比如TriCore的自動上下文保存機制。

#03

主流嵌入式內核

3.1 內核市場現狀

嵌入式常見的內核架構有ARM公司設計的 ARM (Advanced RISC Machine)架構,SiFive公司的 RISC-V (Reduced Instruction Set Computer - Fifth Generation)架構,瑞薩公司的 G4MH 架構,英飛淩的 TriCore 架構等。

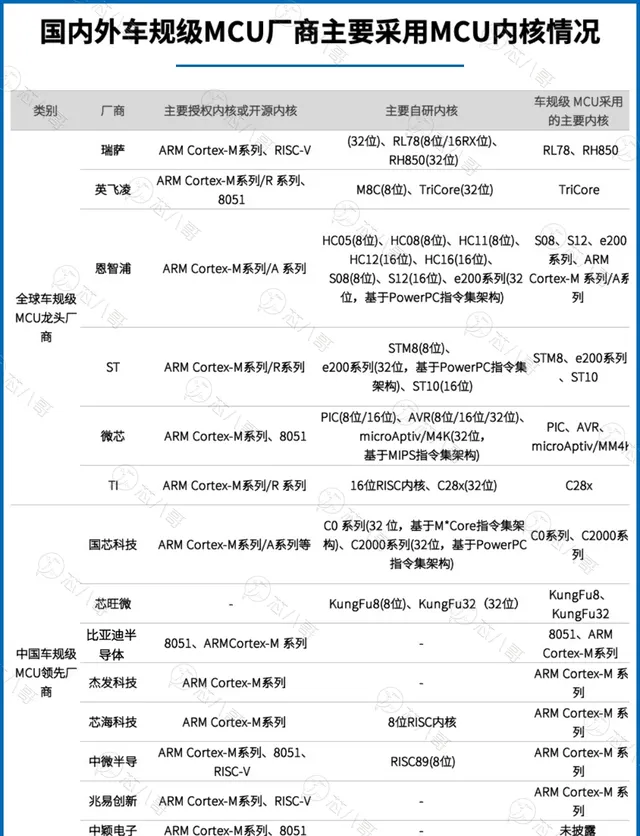

芯片廠商進行芯片研發的模式基本上有三種,一種是購買內核授權進行芯片設計開發,如購買ARM,Synopsys;一種是廠商自行研發內核;還有一種就是開源內核,如RISC-V。下圖列出了當前國內外主流廠商MCU內核使用情況。

資料來源:各公司財報/官網、芯八哥整理

從圖中可以看出,在授權領域各大廠商還是普遍采購 ARM 內核,來進行自家的芯片研發,嵌入式領域使用比較廣泛的還是 ARM Cortex-M 系列。而在開源領域 RISC-V 幾乎是大家的不二之選,經歷了十幾年的發展也逐漸趨於穩定。而在自研內核領域裏,比較廣為人知的要數英飛淩的 TriCore 架構以及瑞薩的 G4MH 架構。

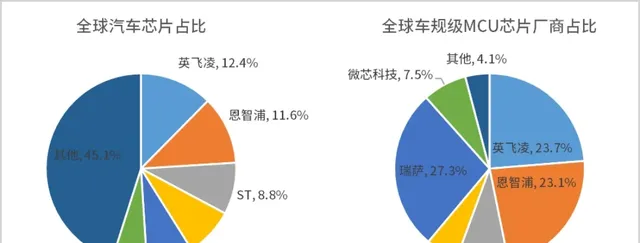

根據統計顯示,車規MCU市場前三家瑞薩、恩智浦、英飛淩占據了余約70%多的份額。

資料來源:各公司財報/官網、芯八哥整理

下面我們介紹以下市場上三類主流的內核架構。

3.2 ARM Cortex-M內核

ARM的歷史可以追溯到1978年,當時Acorn Computers由Chris Curry和Hermann Hauser共同創立。1993年,搭載ARM的諾基亞6110 GSM手機取得了巨大成功,使得ARM7處理器成為ARM的旗艦移動設計,當今全球超過99%的智能電話都基於ARM技術。

隨著公司的發展,ARM的產品線也日益多樣化,2000年代推出了Cortex-A、Cortex-R和Cortex-M CPU處理器。

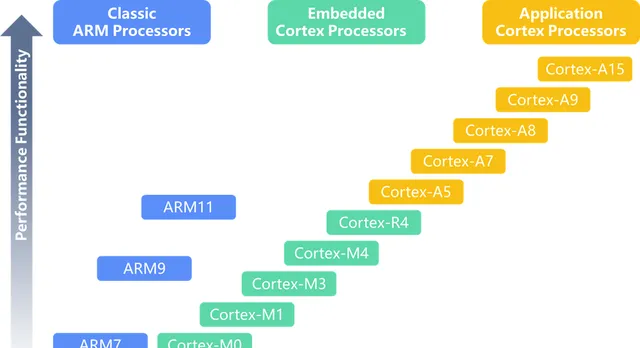

Cortex系列屬於ARMv7架構(ARM公司在經典處理器ARM11以後的產品改用Cortex命名)。包括 Cortex-A、Cortex-M、Cortex-R 等產品。

其中:

下圖為主流Cortex系列產品效能天梯圖。

在車規嵌入式領域,MCU使用的較多的ARM架構就是 Cortex-M 系列,自2004年首款Cortex-M處理器釋出以來,Cortex-M系列已經發展出多個型號,包括Cortex-M0、Cortex-M0+、Cortex-M1、Cortex-M3、Cortex-M4、Cortex-M7、Cortex-M23、Cortex-M33、Cortex-M35P和Cortex-M55等,比較典型的芯片是 STM32 系列、 恩智浦LPC系列 等。

Cortex-M有以下特色:

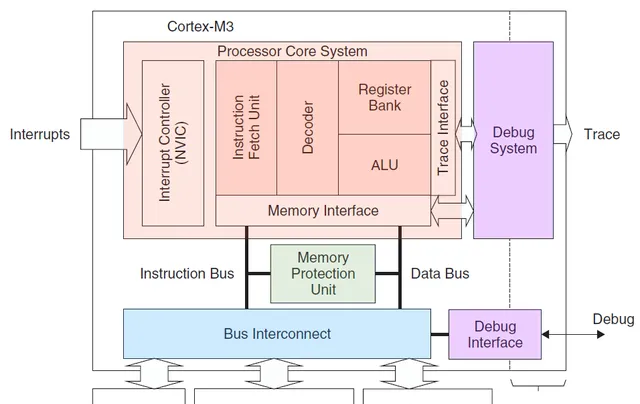

下圖為Cortex-M3內核架構圖。從圖中我們可以看出,Cortex-M內核帶有取指單元、寄存器單元、邏輯運算單元、向量中斷控制器、記憶體介面等。采用程式碼、數據隔離的哈弗儲存結構,是比較典型的電腦內核架構。

Cortex-M系列所用的ArmV7-M指令集,采用的是典型的 load-store 結構指令系統,采用32位元指令系統,同時支持16位元thumb指令。除了常規的運算指令,還支持查表跳轉指令、條件執行、硬件除法指令、乘加指令(MAC)和各種位操作指令,其中Cortex-M7增加了基於FPv5的浮點數據架構,支持額外的浮點指令和可選的雙精度浮點數據處理指令。Cortex-M7采用6級雙發射流水線,提供了更高的效能。

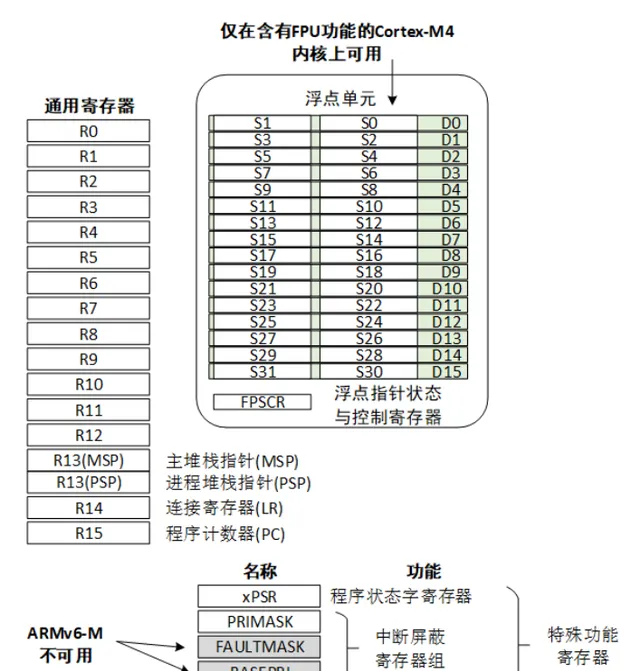

寄存器方面Cortex-M采用16個通用寄存器,和包括程式狀態寄存器xPSR、控制寄存器等在內的特殊功能寄存器。

在內核架構領域,除了Intel,ARM可以說是歷史最悠久的廠商了,數年來的發展奠定了行業的領先地位,基本上是授權內核IP的不二之選。不管是在嵌入式領域還是在移動領域,ARM都具有非常完備的使用者生態,這在芯片領域是至關重要的,因為它意味著較低的開發和風險成本。

3.3 英飛淩TriCore內核

除了ARM這種授權內核以外,有些廠商也會進行自主內核研發,通常是實力雄厚的芯片大廠,比如瑞薩和英飛淩,就是其中的代表。這裏我們以英飛淩為例介紹其TriCore內核。

英飛淩(Infineon Technologies)是一家全球領先的半導體科技公司,總部位於德國,成立於1999年,是西門子集團的半導體部門拆分出來的公司。作為一家技術領域較廣的芯片廠商,其產品線包括功率MOSFET、IGBT、微控制器、傳感器、射頻芯片等。

在微控制器領域,英飛淩的TC2XX系列、TC3XX系列芯片為大家廣泛熟知,在三電、底盤、智駕等領域具有比較高的市場占用率。包括年中剛釋出的TC4XX系列,都是汽車行業的主流選擇。

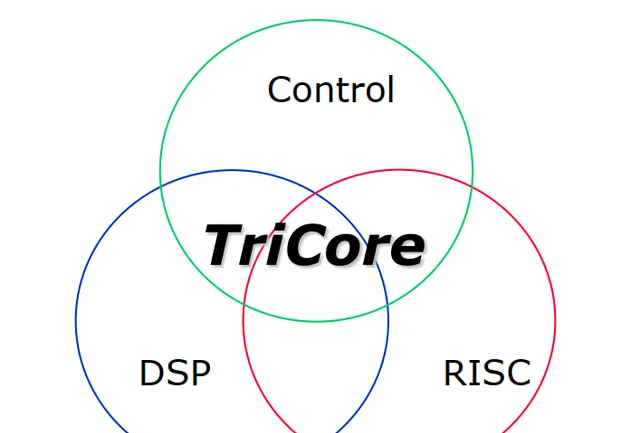

英飛淩Aurix2G TC系列芯片的內核架構是一種 混合架構 ,同時結合了精簡指令集電腦(RISC)和復雜指令集電腦(CISC)的特征,稱為 TriCore內核架構 (以下簡稱TriCore)。它是一款專門為即時性進行了最佳化的32位元的單核(這裏的單核並非指芯片的單核,而是 系統架構只涉及一個核 ,多核之間相互獨立,區別於多核架構)嵌入式系統架構。之所以命名為TriCore,是因為其整合了RISC架構、DSP架構和即時系統的技術於一體,形成了兼具三方優勢的內核架構。

TriCore架構采用了RISC的高效能load/store數據處理模式,同時具有DSP的數據處理能力。TriCore是 32 位電腦系統,因此采用32位元地址空間,支持可選的虛擬地址空間。

下面是TriCore架構的特性:

32位元架構

4GB的地址空間

同時支持16位元和32位元指令,減少程式碼大小

大多數指令在一個周期內執行

分支指令(使用分支預測)

使用並列數據記憶體,實作低中斷延遲與快速自動上下文切換

專用介面特定於應用程式的協處理器,以允許添加客製指令

零開銷回路功能

雙/單時鐘周期,16x16位元乘法累加單元(可選飽和)

可選浮點單元(FPU)和記憶體管理單元(MMU)

廣泛的位處理能力

單指令多數據(SIMD)打包數據操作(2x16位元或4x 8位元運算元)

靈活的中斷優先級方案

字節和位尋址

數據記憶體和CPU寄存器的小端字節排序

記憶體保護

偵錯支持

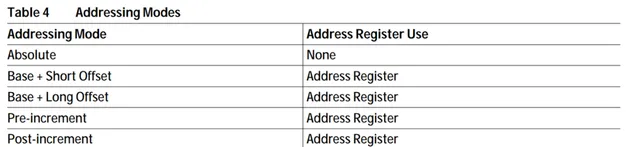

其內核為32位元數據格式,支持C語言中各種基礎數據類別,地址模式采用小端對齊,支持以下尋址模式。

相比於ARM內核,TriCore有兩類通用寄存器,包括16個32位元 數據寄存器 (D[0]~D[15])和16個32位元 地址寄存器 (A[0]~A[15]),數據和地址寄存器的分離促進了算術和記憶體操作並列執行的高效實作。同時,相鄰的兩個奇偶寄存器還可以成對進行存取。

特殊功能寄存器則包括程式計數器PC、程式狀態寄存器PSW、前一個上下文寄存器PCXI和系統控制寄存器。

在ARM中,上下文的內容都是保存在棧中的,當程式進行呼叫時,將通用寄存器和連結寄存器等壓入棧中,等到呼叫返回時,再從棧中彈出,形成一個上下文保存機制。而TriCore內核獨創了一種 硬件上下文切換機制 ,上下文是保存在稱為CSA的一片區域中的,雖然和棧一樣都在RAM中,但是得益於和棧的區分式管理,以及CSA的硬件自動切換機制,能夠有效地提高記憶體使用效率和即時性,以及安全性。

TriCore的指令集采用的也是典型的 load-store 結構,TriCore指令集支持32位元指令和16位元指令,支持嵌入式常用的微控制器系列處理指令,也支持一些DSP數據處理指令。相對於ARM,其指令結構要略復雜一些。

近年來英飛淩持續深耕汽車市場,不斷推陳出新,釋出符合當下電子電器架構設計以及市場需求的汽車MCU芯片,在車規MCU領域有著不可替代的地位。同時英飛淩也不斷努力擴充套件使用者生態,包括舉辦開發者大會、技術峰會,以及和國內高校合作等,這也非常值得國內芯片廠商借鑒和學習。

3.4 RISC-V內核

最後一類內核就是開源內核了,其中的代表就是被大家廣泛采用於自研的RISC-V內核。ARM雖然授權方便,但畢竟面臨著國際政治形式的影響,以及授權費。因此國內芯片一個比較熱門的技術路線,就是基於開源RISC-V進行自研。

RISC-V是一種開源的指令集架構,起源於加州大學柏克萊分校的研究專案。RISC-V是RISC架構的第五代內核,它的發展歷史可以追溯到2010年,當時該校的研究團隊為了設計一款CPU,對比了現有的ARM、MIPS、SPARC和x86等指令集,發現它們不僅復雜,還涉及許多知識產權問題。因此,研究團隊決定開發一套全新的指令集,這就是RISC-V的起源。

隨著技術的發展,RISC-V在嵌入式系統、物聯網、AIOT等領域的套用越來越廣泛,許多企業和研究機構開始采用RISC-V進行產品開發和研究。它的開源特性為全球芯片設計者提供了一個沒有限制、可以自由發揮的平台,預示著RISC-V在未來的技術發展中將扮演越來越重要的角色。

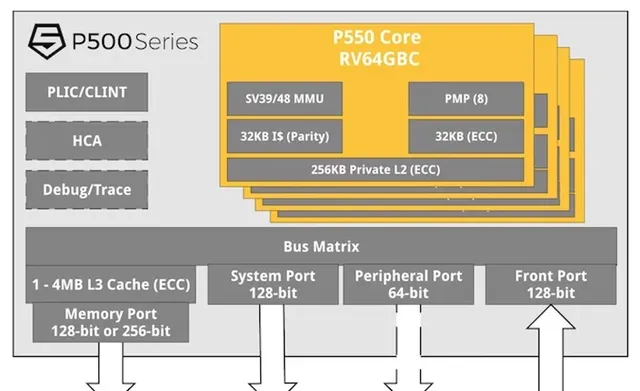

下圖為SiFive公司的一款RISC-V處理器框圖。

RISC-V有以下特點:

RISC-V的指令集包括如下類別:

其指令格式相對比較簡潔,比如ADD rd, rs1, rs2(將rs1和rs2的值相加,結果儲存在rd中)。

RISC-V的指令格式設計使得它能夠高效地在現代處理器中執行,同時保持了足夠的靈活性來支持各種不同的計算任務。這種設計哲學是RISC-V受歡迎的重要原因之一。

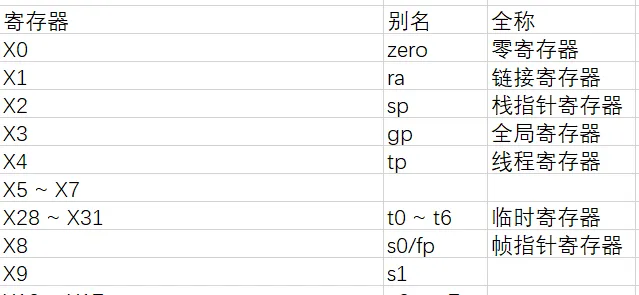

RISC-V的寄存器包括32個通用寄存器,和一系列控制狀態寄存器(CSR)。

2023年3月2日,在玄鐵RISC-V生態大會上,工程院院士倪光南表示,基於RISC-V模組化、可延伸、容易客製、不受壟斷制約等優勢,成為了中國CPU領域最受歡迎的架構。

而芯來科技於2020年釋出了32位元RISC-V架構的NA900系列處理器,並於2023年獲得了ISO 26262最高汽車功能安全等級ASIL D的產品認證,也是國內首家獲得該認證的CPU IP提供商。也是繼ARM、Synopsys之後,全球第三家獲得車規ISO 26262 ASIL D產品認證的CPU IP提供商。

但目前來說,RISC-V內核在車規MCU領域套用還比較少,具有比較大的發展空間。

#04

小 結

當今嵌入式領域中,主流的授權模式內核還是 ARM 系列,這也是國內外芯片廠商選擇最多的IP,也有一些廠商選擇 Synopsys 的車規MCU內核。一些廠商如英飛淩、瑞薩等具有內供自研內核,且相應的芯片在車規領域占有較大的市場。而開源內核架構 RISC-V 異軍突起,被國內外在自研領域有布局的廠商所青睞。

/ END /

招募 | 特約撰稿人(兼職)

添加微信,加入作者交流群

備註公司+姓名(僅限技術專業人士)