繼不久前對外公開展示了面向2nm以下尖端制程制造的High NA EUV光刻機之後,近日,AMSL在其2023年度報告當中還披露了其未來更為先進的Hyper-NA EUV技術的進展,並預計Hyper-NA EUV光刻機可能將會在2030年之際開始商用,為未來更尖端的芯片生產技術提供助力。

ASML目前的EUV工具的數值孔徑(NA)為0.33,可實作13.5nm左右的分辨率,透過單次曝光,可以產生26nm的最小金屬間距和25-30nm尖端到尖端的近似互連空間間距,這些尺寸足以滿足4/5nm節點制程的生產需求。盡管如此,業界仍然需要更小的21-24nm間距的3nm制程工藝,這就是為什麽台積電的N3B制程技術被設計為使用標準EUV雙圖案化技術來實作更小的間距,但這種方法將會相當昂貴。

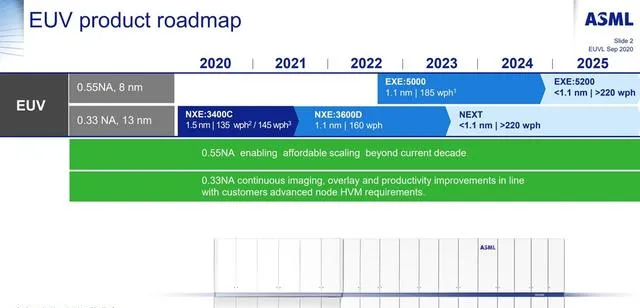

目前ASML已經開始交付的首款High NA EUV系統(EXE:5000)數值孔徑已經由傳統EUV的0.33提升到了0.55,分辨率也由13.5nm提升到了8nm,可以實作16nm的最小金屬間距,對於2nm以下制程節點將非常有用。根據Imec的預計,這即使對於1nm節點技術,High NA EUV系統也能提供解決方案。另外,在生產效率方面,High NA EUV系統每小時可光刻超過 185 個晶圓,與已在大批次制造中使用的 EUV 系統相比還有所增加。ASML還制定了到 2025 年將新一代High NA EUV系統(EXE:5200)的生產效率提高到每小時 220 片晶圓的路線圖。

未來,隨著制程工藝的繼續推進,當進入1nm制程工藝節點之後,晶體管的金屬間距將需要變得更小,屆時晶圓制造商將需要比High NA EUV光刻機更復雜的工具,這也是ASML為何計劃開發出具有更高數值孔徑Hyper NA EUV光刻機的原因。

△根據此前imec的預計,憑借晶體管技術以及先進的制造工具的出現,2030年將進入7埃米(0.7nm)時代,2032年將有望前進演化到5埃米(0.5nm),2036年將有望實作2埃米(0.2nm)。

在2022年之時,Martin就曾指出,ASML正在研究Hyper NA技術的可行性。不過,當時ASML尚未做出最終決定。當時ASML擔憂的是Hyper NA技術的制造成本增長速度和目前High-NA EUV技術一樣,那麽高昂的成為將會使得Hyper NA EUV光刻機在經濟層面幾乎不可行。

要知道目前全球僅剩下了台積電、三星、英特爾這三家尖端邏輯制程芯片制造商,雖然日本的Rapidus可能會發展成為新的玩家,但即便如此,這個領域的玩家已經是非常的少了。

根據資料顯示,ASML標準數值孔徑的EUV光刻機(NXE系列)目前售價約為1.83億美元,而High NA EUV光刻機(EXE:5000)的售價約為3.8億美元,增長了一倍多,如果Hyper NA EUV光刻機成本也將繼續增長一倍,一台價格就將超過7.6億美元,這樣的價格即便是台積電、三星、英特爾這樣的巨頭恐怕也難以承受。

不過,從ASML 2023年年度報告中披露的資訊來看,ASML似乎已經解決了Hyper NA EUV的成本和交付周期問題。

ASML技術長Martin van den Brink在ASML 2023年年度報告中表示,NA值高於0.7的Hyper NA光刻機無疑是繼續發展芯片生產技術的機會,預計將從2030年左右開始獲得套用。Hyper-NA光刻可能與邏輯制程芯片更相關,並且將提供比High NA EUV光刻雙重圖案化更實惠的解決方案,同時對於DRAM制程來說也是一個機會。

「對我們來說,關鍵是Hyper NA正在推動我們的整體EUV平台能力,進一步最佳化了成本和交付周期。就整個行業而言,數碼化將繼續推動許多正在改變我們的解決方案。盡管像我們的EUV平台這樣的系統需要大量的能源,但我認為,我們透過開發智能電網和電動汽車等技術,為減少溫室氣體排放做出了積極貢獻。未來,更多這樣的技術將隨之而來。」Martin說道。

編輯:芯智訊-浪客劍