什麽是雪崩擊穿?

MOSFET在電源板上由於母線電壓、漏感尖峰電壓等系統電壓疊加在MOSFET漏源之間,當該電壓超過MOSFET絕對最大額定值BVDSS的電壓時,就會發生擊穿,並且超過達到了一定的能力從而導致MOSFET失效。簡而言之就是由於MOSFET漏源極的電壓超過其規定電壓值並達到一定的能量限度而導致的一種常見的失效模式。

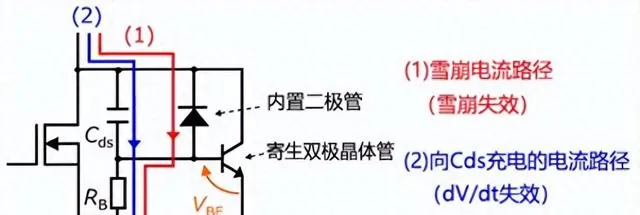

當施加高於BVDSS的高電場時,自由電子被加速並帶有很大的能量。這會導致碰撞電離,從而產生電子-電洞對。這種電子-電洞對呈雪崩式增加的現象稱為「雪崩擊穿」。在這種雪崩擊穿期間,與 MOSFET內部二極管電流呈反方向流動的電流稱為「雪崩電流Ias」,參見下圖1。

圖1-雪崩電流Ias

雪崩失效:短路造成的失效

如圖1所示,Ias會流經MOSFET的基極寄生電阻RB。此時,寄生雙極型晶體管的基極和發射極之間會產生電位差VBE,如果該電位差較大,則寄生雙極晶體管可能會變為導通狀態。一旦這個寄生雙極晶體管導通,就會流過大電流,MOSFET可能會因短路而失效。

雪崩失效:熱量造成的失效

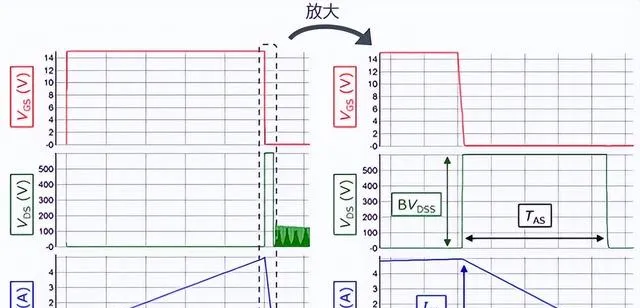

在雪崩擊穿期間,不僅會發生由雪崩電流導致寄生雙極晶體管誤導通而造成的短路和損壞,還會發生由傳導損耗帶來的熱量造成的損壞。如前所述,當MOSFET處於擊穿狀態時會流過雪崩電流。在這種狀態下,BVDSS被施加到MOSFET並且流過雪崩電流,它們的乘積稱為率損耗。這種功率損耗稱為「雪崩能量Eas」。雪崩測試電路及其測試結果的波形如圖2和圖3所示。

圖2-雪崩測試電路及波形

圖3-雪崩測試放大波形

雪崩能量公式

等式1:Ias^2 * Tas = constant = K-rated

等式2:Tas = (L * Ias) / (1.3*BVDSS)

等式2代入等式1,得Ias^2 * (L * Ias) / (1.3*BVDSS) = constant = K-rated

即等式3:Ias^3 * L = (1.3*BVDSS) * K-rated

等式4:Eas=Pas * Tas = 0.5* (1.3*BVDSS) * Ias * Tas

等式2代入等式4,

得等式5:Eas= 0.5* (1.3*BVDSS) * Ias *(L * Ias) / (1.3*BVDSS) =0.5 * L * Ias^2

Eas:雪崩能量,BVDSS:MOS擊穿電壓,Ias:雪崩電流,Tas:雪崩時間,L:寄生電感

1)若已知Ias,BVDSS,K-rated,可求Tas,L,Eas; 以HUF76407D3為例,Ias=9A,BVDSS=78V,K-rated=0.00913,

根據等式1,可求出Tas=0.112ms;

根據等式2,可求出L=1.0mH;

根據等式5,可求出Eas=40mJ;

2)若已知L,BVDSS,K-rated,可求Ias,Tas,Eas;以HUF76407D3為例,L=1.0mH,BVDSS=78V,K-rated=0.00913,

根據等式3,可求出Ias=9A;

根據等式2,可求出Tas=0.112ms;

根據等式5,可求出Eas=40mJ;

雪崩失效的預防措施:

一般情況下,有抗雪崩保證的MOSFET,在其規格書中會規定IAS和EAS的絕對最大額定值,因此可以透過規格書來了解詳細的值。在有雪崩電流流動的工作環境中,需要把握Ias和Eas的實際值,並在絕對最大額定值範圍內使用。

引發雪崩擊穿的例子包括寄生電感引起的浪湧電壓,建議改用引腳更短的封裝的MOSFET、改善電路板布局以降低寄生電感、合理降額使用等都是比較有效的措施。