在追求高效能電子器件的今天,碳化矽以其卓越的物理和電學效能,成為了制造電力電子器件的理想材料。然而,碳化矽襯底在 拋光工藝 上還面臨著成本、環保等方面的難題,一直是制約其廣泛套用的瓶頸。

傳統CMP(化學機械拋光)需要使用大量的 拋光液材料 ,拋光液成本占拋光環節成本比例較大,這不僅增加了 生產成本 ,也對 環境 造成了負擔。

近日,日本立命館大學(Ritsumeikan University)一研究團隊開發了一種新型的 ECMP(電化學機械拋光) 技術,可帶來3大技術優勢:

● 環保高效:ECMP技術避免了使用有害的液體化學物質,減少了對環境的影響;

● 高材料去除率:該技術實作了約15µm/h的材料去除率(MRR),是傳統CMP的 10倍 。

● 表面質素高:透過ECMP處理的碳化矽襯底表面光滑,粗糙度可降至亞納米級別。

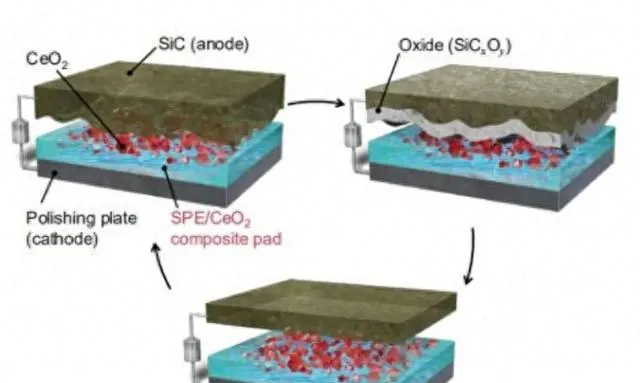

采用ECMP進行的材料去除工藝示意圖

獲取該文獻,請加許若冰hangjiashuo999,詳情請往下看:

技術原理

電化學機械拋光是一種新型的襯底表面處理技術,在ECMP過程中,碳化矽襯底作為陽極,與拋光板(陰極)之間夾著 SPE/CeO2復合材料襯墊 。當施加偏置電壓時,碳化矽表面與SPE發生電解反應,形成一層易於去除的氧化膜,這層氧化膜隨後被襯墊中的CeO2顆粒去除。

ECMP拋光裝置的示意圖

具體實驗驗證:

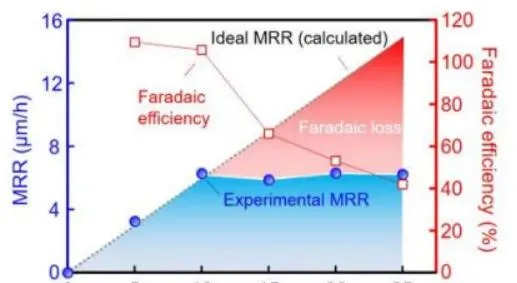

在實驗過程中,研究團隊首先研究了 電解電流密度 對碳化矽襯底材料去除率的影響,發現MRR與電解電流密度成正比,且在一定的電流密度下達到飽和:

● 在電解電流密度低於10 mA/cm²時,MRR隨電流密度的增加而增加,法拉第效率 接近100% 。

● 超過15 mA/cm²後,MRR達到飽和狀態,法拉第效率開始下降,表明電流密度的進一步提高並沒有帶來更高的材料去除效率。

電解電流密度對ECMP的碳化矽(0001)的MRR和法拉第效率的影響

隨後,他們進一步的實驗探討了 機械條件 ,即拋光壓力和旋轉速率的乘積(P×RR),對MRR的影響。實驗在恒定的電解電流密度(25 mA/cm²)下進行:

● MRR隨著機械條件的增強而線性增加,在最高的機械條件下幾乎達到了法拉第電解定律預測的理想MRR值(14.8 µm/h)。

● 這一結果表明,在較高的機械條件下,CeO2顆粒更有效地去除氧化膜,減少了碳化矽表面形成的氧化物層的厚度,從而 提高了法拉第效率 。

ECMP的機械條件(MC)對碳化矽(0001)的MRR的影響

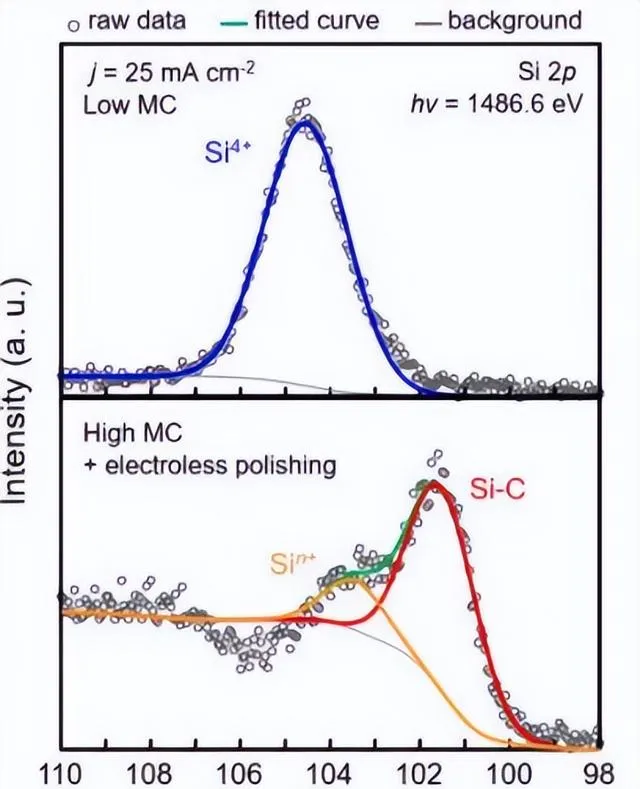

此外,研究團隊利用X射線光電子能譜(XPS)分析了不同ECMP條件下處理的表面,結果顯示在高機械條件下,經過ECMP和隨後的無電解拋光,Si 2p光譜中沒有明顯的Si4+峰,表明表面殘留的氧化物 被有效去除 。

最後,研究團隊進行了襯底表面形貌和粗糙度觀察以及均勻性評估,結果如下:

● ECMP處理6分鐘後,表面粗糙度從50 nm Sa顯著降低到0.68 nm Sa,顯示出 非常光滑 的表面。

● 在低電解電流密度下進行ECMP處理,然後進行無電解拋光,可以獲得粗糙度為0.084 nm Sa的 超光滑表面 。

ECMP對碳化矽表面形態的改變(左)、經ECMP處理的碳化矽(0001)表面的AFM影像(右)

● 所開發的ECMP方法能有效地在整個晶片上均勻去除SiC表面,獲得平均粗糙度低至 0.68 nm 的光滑表面。

實驗驗證表明,ECMP技術不僅提高了碳化矽襯底的拋光效率,而且透過精確控制電解和機械條件,實作了表面粗糙度的顯著降低和表面質素的大幅提升,為碳化矽襯底的綠色制造提供了強有力的技術支持。

來源: 行家說三代半

*聲明:本文由作者原創。文章內容系作者個人觀點,寬禁帶半導體技術創新聯盟轉載僅為了傳達一種不同的觀點,不代表本聯盟對該觀點贊同或支持,如果有任何異議,歡迎聯系我們。