高速先生成員--姜傑

端接可以解決很多反射問題,如果還有問題,有沒有一種可能是端接電阻阻值沒選對?

對於點到點的拓撲,末端並聯電阻的阻值比較容易選擇,端接電阻阻值R與傳輸線特征阻抗一樣即可。

VTT為1V時,端接電阻R分別取30ohm,50ohm,70ohm的接收端電壓如下圖:

可以發現,R與傳輸線特征阻抗同樣都是50ohm時,接收端訊號基本沒有反射。原因是接收器輸入阻抗通常很高,從訊號的角度看,傳輸到末端的訊號感受的阻抗就是端接電阻的阻值,R與傳輸線特征阻抗的匹配消除了阻抗突變引起的反射。

不幸的是,目前的絕大多數DDR的地址控制訊號都是一驅多的拓撲,於是,問題開始變的復雜。

明明DDR的數據訊號速率更高,為啥要更關註DDR的地址控制訊號?數據訊號一般都是點到點的拓撲,而且大多有片上端接(ODT),走線拓撲簡單加上端接加持,訊號質素通常都比較有保障。而DDR的地址控制類訊號的設計難度在於其拓撲的復雜性,一驅多的走線拓撲對訊號質素的影響太大,即便速率相比數據訊號減半。

為了讓大家對端接電阻的作用感受更加明顯,我們選擇了一個難度較大的案例:一驅九的DDR4地址訊號,速率1600Mbps。

由於反射更容易在近端顆粒DRAM1/DRAM2處積累,該處的訊號質素更容易成為瓶頸。

方便對比,先看看不加端接的近端DRAM1訊號。

和預料的一樣,波形是雜亂的,眼圖是閉合的。

再來看看按照原設計的39ohm端接電阻,近端顆粒訊號質素有什麽變化。

顯而易見,波形質素有了較大改善,眼睛也睜開了。但還是會有部份波形落在閾值電平(VIH:690mV;VIL:510mV)的區間內,這種情況下的時序大概率是Fail的。

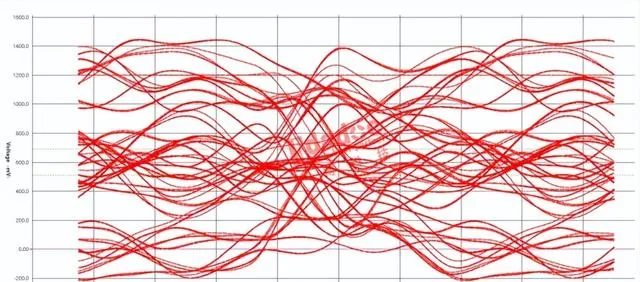

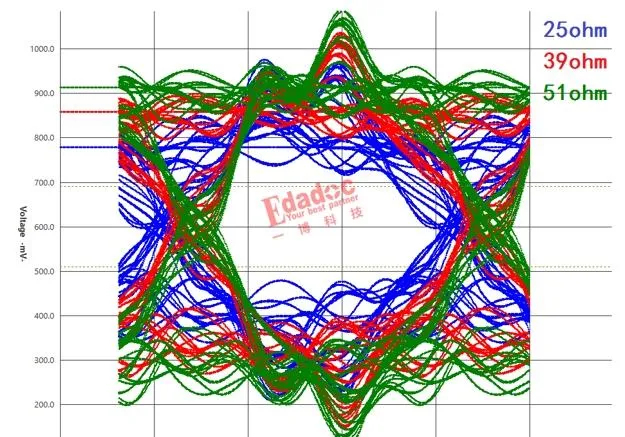

下面掃描三種端接電阻阻值:25ohm,39ohm和51ohm,近端顆粒訊號的波形對比如下:

可以發現,按照這三種阻值的從大變小,訊號質素是逐漸改善的。

對眼圖的睜開程度進行對比,這種趨勢會看的更加明顯。

為了能看的更清楚,將三個眼圖在時間軸上展開進行對比。

以閾值電平(VIH:690mV;VIL:510mV)作為判決標準,25ohm端接電阻的眼圖可以滿足要求,另外兩個則不達標。

當然了,這是個多負載的拓撲,其它DDR上的訊號也需要關註。透過對比,高速先生發現了一個有趣的現象,同樣的阻值變化,遠端顆粒DRAM9上的訊號質素變化與近端顆粒正好相反。

好在遠端DDR由於更靠近端接電阻,訊號裕量更大,因此可以「損有余而補不足」,即便選擇遠端波形最差的25ohm,眼圖也是可以滿足閾值電平要求的。

那是不是所有的一驅多DDR地址控制訊號,隨著端接電阻阻值變化都有相同的趨勢呢?僅透過這一個案例,高速先生也無法給出一般性的結論。唯一可以肯定的是:前途是光明的,道路是曲折的,阻值是不確定的。拓撲越復雜,速率越高,就越有必要透過仿真確定最優端接電阻阻值。

問題來了

大家知道的最佳化DDR地址控制訊號質素的方法都有哪些?

關於一博:

一博科技成立於2003年3月,深圳創業板上市公司,股票程式碼: 301366。專註於高速PCB設計技術服務、研發樣機及批次PCBA生產服務。致力於打造一流的硬件創新平台,加快電子產品的硬件創新行程,提升產品質素。

我司在海內外設立十余個研發機構,全球研發工程師700余人。一博全資持有的PCBA總廠位於深圳,並在珠海、上海、成都、長沙、天津設立分廠,配備全新進口富士NXT3多功能貼片機、XPF多功能貼片機、AIMEX III高速貼片機、全自動錫膏印刷機、十二溫區無鉛(氮氣)回流爐、波峰焊等高端器材,並配有線上 3D AOI、3D XRAY、3D SPI、智能首件測試儀、全自動分板機、BGA返修台、ICT、選擇性三防漆等器材,專註高品質的研發快件、批次的SMT貼片、組裝等服務。作為國內首批SMT快件廠商,48小時準交率超過95%。常備12萬余種常用電子元器件現貨在庫,並提供全BOM元器件服務。

PCB設計、制板、貼片、物料一站式硬件創新平台,縮短客戶研發周期,方便省心。

EDADOC, Your Best Partner.