設計低功耗微控制器(MCU)是一項復雜的任務,為特定嵌入式設計挑選合適的MCU同樣充滿挑戰。涉及的套用特定考慮因素繁多,使得對比微控制器的技術規格成為一項艱巨的工作。

從系統架構的視角出發,為了確定哪些MCU真正符合「低功耗」的標準,設計師需要對半導體供應商提出的各種聲明進行仔細篩選。由於不同供應商采用了不同且經常令人困惑的度量標準,這項任務並不簡單。

MCU的電源消耗通常可以分為以下幾個部份:

總耗電量 = 工作模式功耗 + 待機(休眠)模式功耗

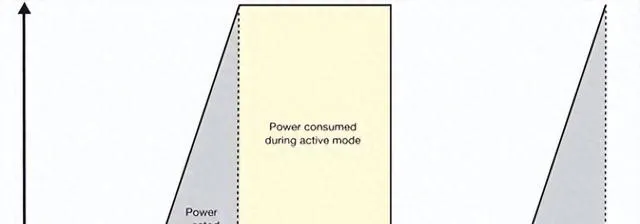

然而,另一個需要考慮的重要標準是MCU從待機狀態到工作狀態的轉換時間。 MCU開始執行有用的處理是在所有數碼和模擬元件完全穩定並開始執行後,因此在計算總耗電量時,這部份(浪費的)能量也應該被包括在內:

總耗電量 = 工作模式功耗 + 待機(休眠)模式功耗 + 喚醒功耗

由於每個套用的需求不同,系統設計師可能會更關註這些元素中的某些。例如,像水表這樣的套用,大部份時間處於待機狀態,因此它們的長期工作周期顯然需要非常低的待機功耗。而像數據記錄器這樣的套用,頻繁地進入和結束工作狀態,因此限制喚醒轉換中消耗的時間變得至關重要。 值得註意的是,專門為MCU開發解決方案的制造商不會試圖猜測哪個指標最重要,而是從底層開始設計,致力於最小化上述公式中的每一個部份。為此,需要強大的混合訊號技術基礎,以解決在模擬和數碼領域最小化功耗所面臨的架構級和電路級挑戰。 探討這些變量可以幫助突出系統設計師在選擇最佳MCU解決方案時需要了解的問題類別。

工作模式功耗

對於CMOS邏輯門,動態功耗可以用以下公式表示:

工作模式功耗 = C x V^2 x f

其中C代表負載電容,V代表供應電壓,f代表開關頻率。

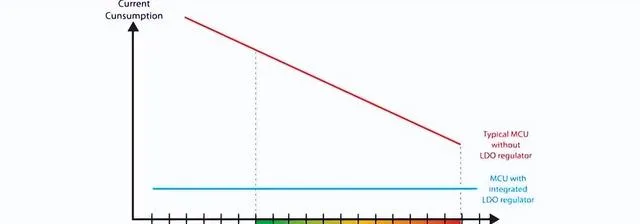

電容項取決於設計和處理技術,而頻率項取決於套用的處理需求。然而,正如公式所示,供應電壓對MCU總體功耗有著顯著的影響。因此, 在MCU設計中加入電壓調節功能可以透過為MCU電路提供更低的穩定供電,從而節省大量的工作模式功耗。 開關型轉換器可能是一種解決方案,但它們最適合大電壓轉換比的調節環境。對於電池供電的套用(在電池壽命結束時,平均電壓轉換比較小,接近1:1),更好的解決方案可能是整合一個片上低壓降(Low Drop Out, LDO)線性電壓調節器,因為它以較低的復雜性和成本提供可接受的效率,而不是開關解決方案。

為了強調使用LDO調節器的優勢,我們可以重新審視CMOS動態功耗方程式:

工作模式功耗 = C x V^2 x f

= V x (C x V x f)

= V x I,其中動態電流I = C x V x f

動態電流通常對於頻率1MHz和特定供應電壓進行標準化。例如,一種新型的超低功耗MCU,在1.8V電壓下的動態電流消耗為160µA/MHz。如果沒有電源調節,當供電電壓為3.2V時,這個數值會增加到(160) x (3.2/1.8) = 284 µA/MHz。使用LDO的情況下,電池電流在整個供應範圍內都將保持在160µA/MHz。

正如所見,這種 高級電源架構可以在整個工作電壓範圍內保持恒定的工作電流,幫助系統設計師顯著節省功耗。因此,對於系統設計師來說,確定MCU在整個工作電壓範圍內的電流消耗是非常重要的 ——而不僅僅是供應商經常參照的1.8V的最低工作條件。參照一個樂觀的電流值,假設電壓供應不低於典型值,這並不能準確反映真實世界中的套用環境。例如,在2 x AA/AAA和硬幣電池套用中,電池在其生命周期的大部份時間內都是在接近初始3V的電壓下工作的,如果僅參照1.8V的規格,可能會讓人誤以為MCU的功耗比經常參照的數值要高出約50%。

此外,由於功耗與開關頻率成正比, 對於系統設計師來說,將參照的電流值歸一化到每MHz的電流是很重要的。 將這兩個因素結合起來,可以進行MCUs的並列對比,基於以下指標:

3V下的電流消耗/MHz

一些供應商可能會試圖透過將「MHz」等同於系統時鐘速度來混淆概念,而實際有意義的是指令時鐘速度。這是誤導性的,因為時鐘速度可以以雙倍(或更多)的實際指令速度執行,從而使功耗效率加倍(或更多)。因此, 需要確保所有數值都歸一化到指令時鐘速度。這樣做,再加上使用典型的供應電壓,可以正確推匯出實際的工作模式電流消耗預算。

待機(休眠)電流

為了實作最大的能源效率(和電池壽命),需要確保MCU的每個任務在盡可能短的時間內完成,以盡可能低的電流和電壓消耗最少的電能,讓器材大部份時間都處於極低功耗的休眠模式。 在某些套用中,休眠模式的電流是影響總能源消耗的主要參數。然而,經常被忽略的一點是,MCU可以達到的最低休眠電流主要受到其漏電流的限制。 例如,一個有20個輸入的器材,如果每個輸入的漏電流規格為100nA,那麽在休眠模式下可能會消耗高達2µA的電力。

漏電流受多種因素影響,但最重要的是采用的底層工藝技術。有時,供應商會選擇使用0.25或0.35微米的工藝技術來減少漏電所引起的休眠電流,但這種選擇會導致更高的工作電流。在其他情況下,MCU供應商可能會選擇使用0.18微米或更小的工藝技術以減少工作模式電流,但這會帶來更高的漏電電流。 解決這一問題的獨特方法是,無論采用何種底層工藝技術,利用混合訊號專業技術實作一個專門設計的高級電源管理單元(PMU),以限制漏電,並實作超低休眠電流。

在采用0.25微米或更小的工藝技術時,要實作最小的休眠模式電流,需要切斷給數碼核心的電源。 在休眠模式下執行的模組,如電源管理電路,I/O墊環元件和即時時鐘,必須從未調節的電源電壓執行,以避免在LDO中消耗額外的電流。 切斷數碼核心電源也可以防止其關態漏電導致的休眠模式電流;然而,MCU需要在休眠模式下保留所有RAM內容和所有寄存器狀態,以便程式碼執行能夠恢復到中斷點。 這種保留可以透過一種非常低電流的休眠模式鎖存偏置方案實作,或者使用特殊的保持鎖存,這些鎖存在休眠模式下無顯著漏電。 MCU還需要一種形式的連續供電電壓檢測(即「斷電檢測」),如果供應電壓下降到最小保持電壓以下,則復位器材,因為這可能導致狀態損壞。

因此,從系統設計師的角度來看,檢查底層漏電流規格非常重要,以確定哪些MCU供應商利用他們的混合訊號專業知識來解決這個復雜問題。設計師還應該意識到,大多數供應商提供多種不同的待機電流選項。大多數供應商強調他們的最低休眠模式電流,這通常是在即時時鐘和斷電檢測器被禁用時的電流。有些供應商甚至會引述關機模式電流,這種模式不保留記憶體,並需要重設才能喚醒,這通常並不實用。因此, 由於大多數套用需要完整的RAM和寄存器保持,對於系統設計師來說,基於以下度量標準進行比較是很重要的:

- 休眠/待機模式下的電流,即時時鐘和斷電檢測器禁用(保持RAM)

- 待機/休眠模式下電流,即時時鐘禁用,斷電檢測器啟用

- 待機/休眠模式下電流,即時時鐘和斷電檢測器都啟用

這樣,系統設計師就可以在計算基於其套用的工作周期的整個待機模式的電源預算時,使用正確的數值。

喚醒能量

正如前面所述,在使用休眠模式的系統中,喚醒MCU和準備它采集或處理數據時可能會浪費大量電源。實際上,在某些套用中,MCU從待機狀態恢復時消耗的能量與完全處理數據時使用的能量相當。因此,設計MCU時要能夠在極短的時間內喚醒並穩定,以最大限度地減少處於浪費電能狀態的時間。

MCU應該能夠從外部事件或內部定時器喚醒結束休眠模式。最靈活的周期性喚醒源是即時時鐘,它既可以從外部晶體振蕩器(對於需要精確計時的套用)執行,也可以從一個低頻的內部振蕩器(適合對精度要求不高的套用)執行。 避免使用啟動慢的晶體振蕩器作為高速系統時鐘;一個精確、快速啟動的片上振蕩器是更好的選擇。

此外, 由於許多產品定期喚醒以使用片上ADC采樣輸入,需要足夠時間讓數碼電路喚醒,模擬電路穩定後才能開始有效測量。 模擬模組的啟動行為可能對活動模式時間有重大影響;使用外部去耦電容的電壓調節器或參考可能需要數毫秒時間才能穩定。有時,MCU供應商只引述數碼電路的喚醒時間,而忽略了模擬電路穩定所需的時間。因此, 對於系統設計師來說,分析模擬電路和數碼電路的整體喚醒和穩定時間,以計算這部份浪費電能的真實成本是非常重要的。

其他考慮因素

還有其他方式可以進一步減少系統中的功耗。例如,MCU通常可以在1.8V甚至更低的電壓下工作(在這種情況下可能沒有ADC功能;指令時脈降低),因此經常使用2 x AA/AAA電池配置。一種創新的減少功耗(和環境影響)的方法是將設計轉換為單電池配置,其中電池可以一直使用到其壽命盡頭(0.9V)。 為了實作這一點,MCU必須整合一個高度最佳化的直流-直流轉換器 ,能夠使用到電池的最低工作電壓,對於堿性電池來說是0.9V。這種方法也可以節省供應商和/或消費者在電池上的開銷。

減少功耗的另一種方法是使用高度整合的MCU,包括ADC、DAC和其他外設 ,因為套用可以控制啟用和禁用這些外設。例如,有些MCU提供了專門的低功耗ADC,帶有突發模式,該模式可以在CPU關閉時采取模擬測量,以進一步減少功耗。

對於大多數套用來說,可能最好的方法是簡單地返回到初始的功耗方程式,以便切入主題:

總功耗 = 工作模式功耗 + 待機模式功耗 + 喚醒功耗

每個套用將實際套用由待機功耗,工作模式功耗,和喚醒功耗等各種元素的組合影響,因此,系統設計師可能會發現,開始任何分析最有幫助的方式是把功耗數值系統地分解為上面的元素。 一旦得到了這些數值,系統設計師又可以考慮套用的工作周期——套用預期在待機,工作,和喚醒模式下,花費各比例的時間——以計算出平均功耗的數值。得到的數值應該給系統設計師一個近似的,可用來客觀評價和對比MCU選項以達到最低可能的系統級功耗的值。