9月3日,在SEMICON Taiwan 2024 展會期間的「異質整合國際高峰論壇」上,SK 海麗仕封裝(PKG)研發副社長李康旭(Kangwook Lee)以「準備AI 時代的HBM和先進封裝技術」為題,分享了SK 海麗仕最新的HBM技術。

SK海麗仕的HBM規劃

李康旭指出, HBM 是克服「儲存墻」(Memory Walls)的最優解決方案,基於其強大的I/O 並列化能力,使HBM 成為Al 系統中用於訓練和推理的最高規格DRAM。

根據套用產品(Application)不同,使用的HBM數量也不同。隨著HBM技術的發展,在訓練和推理AI 伺服器中搭載HBM 平均數量也會增加,如近期訓練伺服器套用需要8 個HBM3E,推理則只需要4-5 個,長遠估算可能分別要12 個和8 個HBM4 /HBM4E。

李康旭表示,SK 海麗仕計劃在2025 年推出12 層的HBM4 產品,透過自家研發的封裝技術,在HBM 產品的能效和散熱效能上更具競爭力。

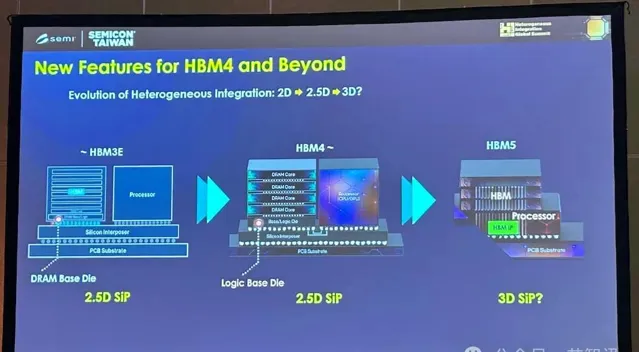

有趣的是,SK 海麗仕到HBM3E 仍是DRAM 基礎裸片(Base Die),采用2.5D 系統級封裝,到HBM4 考慮將DRAM Base Die 改成Logic Base Die,使效能和能效獲得進一步提升。此外,到了HBM5 架構可能再次改變,SK 海麗仕目前正評估包括2.5D 和3D 系統級封裝(SiP)在內的各種方案。

提到未來HBM 技術挑戰,李康旭表示在封裝、設計面臨許多挑戰,以封裝來說是堆疊數限制,更希望直接結合邏輯芯片和HBM 堆疊,客戶目前也對3D SIP 感興趣,因此3D SIP、儲存芯片頻寬、結合客戶需求和協作,都是未來挑戰之一。

對於一些新創AI芯片公司出於成本考慮,采用增大片上SRAM來減少對於HBM的依賴的做法,李康旭認為,這主要仍取決於產品套用,有些公司宣稱HBM 太貴,所以找尋其他不需要HBM 的解決方案,但仍需要看具體情況,高效能計算產品仍需要HBM ,但某些套用可能不需要有HBM,主要仍取決於套用場景。

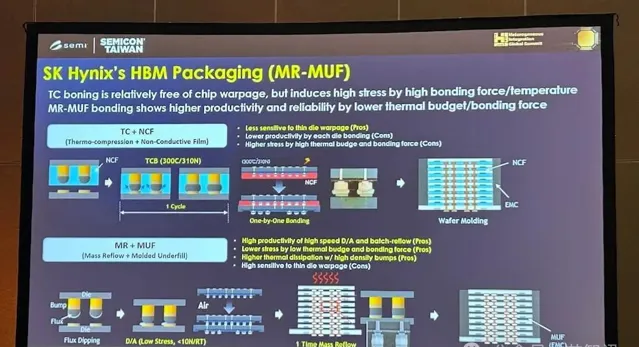

兩種封裝路線:MR-MUF 和Hybrid Bonding

SK 海麗仕目前的HBM 產品主要采用MR-MUF 封裝技術,具有低壓、低溫鍵合和批次熱處理的優勢,在生產效率和可靠性優於TC-NCF 制程。此外,具有高熱導特性的Gap-Fill 材料(填充空隙的材料)和高密度金屬凸塊(在垂直堆疊HBM DRAM時起連線電路作用的微小鼓包型材料)的形成,散熱可比TC-NCF 制程有36% 效能優勢。

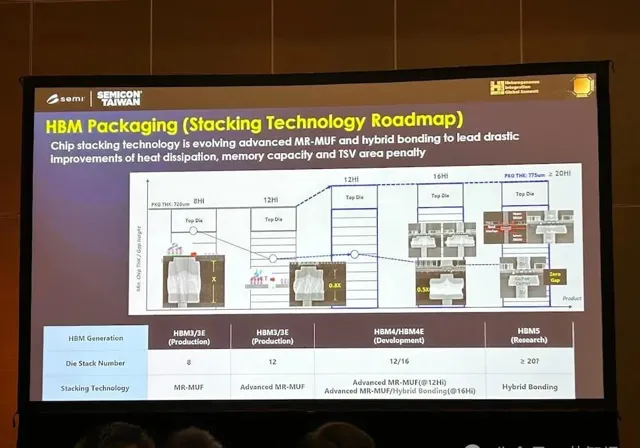

但是由於堆疊將面臨高度限制,目前SK 海麗仕不斷找尋新方法,在有限高度下塞入更多堆疊層數。李康旭指出,公司8 層HBM3/HBM3E 使用MR-MUF技術;12層HBM3/HBM3E 將采用Advanced MR-MUF技術;明年下半年準備出貨的12 層HBM4 同樣采Advanced MR-MUF 技術;至於後續的16 層HBM4/ HBM4E 將同步采用Advanced MR-MUF 和混合鍵合(Hybrid Bonding)兩種技術,未來堆疊20 層以上產品(如HBM5)則將轉向Hybrid Bonding 前進。

李康旭指出,SK海麗仕目前正在研發16 層產品相關技術,最近確認對16 層產品仍可適用Advanced MR-MUF技術的可能性。此外,SK海麗仕此前也表示,從HBM4E 開始會更強調「客製化HBM」,以應對各種客戶需求,如提升芯片效率。

李康旭解釋,標準HBM 和客製化HBM 核心芯片相同,但是Base Die(基礎芯片)不同,主要是再加入客戶的IP,芯片效率也可能更高。

另據韓媒報道,SK 海麗仕將小芯片技術(chiplet)匯入儲存控制器(memory controller)。對此,李康旭表示目前控制器是在單芯片(SoC)中,但未來會針對小芯片封裝技術,結合儲存控制器。除了HBM 外,SSD 的SoC 控制器也會采用這項技術。

編輯:芯智訊 -浪客劍 綜合自Technews